Itanium

| |

| General information | |

|---|---|

| Launched | June 2001[a] |

| Discontinued | January 30, 2020[1] |

| Marketed by | Intel |

| Designed by | Intel Hewlett-Packard |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 733 MHz to 2.66 GHz |

| FSB speeds | 266 MT/s to 667 MT/s |

| QPI speeds | 4.8 GT/s to 6.4 GT/s |

| Data width | 64 bits |

| Address width | 64 bits |

| Virtual address width | 64 bits |

| Cache | |

| L1 cache | Up to 32 KB per core (data) Up to 32 KB per core (instructions) |

| L2 cache | Up to 256 KB per core (data) Up to 1 MB per core (instructions) |

| L3 cache | Up to 32 MB |

| L4 cache | 32 MB (Hondo only) |

| Architecture and classification | |

| Application | High-end/mission critical servers High performance computing High-end workstations |

| Technology node | 180 nm to 32 nm |

| Microarchitecture | P7 |

| Instruction set | IA-64 |

| Extensions | |

| Physical specifications | |

| Cores |

|

| Memory (RAM) | |

| Packages |

|

| Sockets | |

| Products, models, variants | |

| Core names |

|

| Models |

|

| Support status | |

| Unsupported | |

Itanium (/aɪˈteɪniəm/; eye-TAY-nee-əm) is a discontinued family of 64-bit Intel microprocessors that implement the Intel Itanium architecture (formerly called IA-64). The Itanium architecture originated at Hewlett-Packard (HP), and was later jointly developed by HP and Intel. Launched in June 2001, Intel initially marketed the processors for enterprise servers and high-performance computing systems. In the concept phase, engineers said "we could run circles around PowerPC...we could kill the x86." Early predictions were that IA-64 would expand to the lower-end servers, supplanting Xeon, and eventually penetrate into the personal computers, eventually to supplant reduced instruction set computing (RISC) and complex instruction set computing (CISC) architectures for all general-purpose applications.

When first released in 2001 after a decade of development, Itanium's performance was disappointing compared to better-established RISC and CISC processors. Emulation to run existing x86 applications and operating systems was particularly poor. Itanium-based systems were produced by HP and its successor Hewlett Packard Enterprise (HPE) as the Integrity Servers line, and by several other manufacturers. In 2008, Itanium was the fourth-most deployed microprocessor architecture for enterprise-class systems, behind x86-64, Power ISA, and SPARC.[6][needs update]

In February 2017, Intel released the final generation, Kittson, to test customers, and in May began shipping in volume.[7][8] It was only used in mission-critical servers from HPE.

In 2019, Intel announced that new orders for Itanium would be accepted until January 30, 2020, and shipments would cease by July 29, 2021.[1] This took place on schedule.[9]

Itanium never sold well outside enterprise servers and high-performance computing systems, and the architecture was ultimately supplanted by competitor AMD's x86-64 (also called AMD64) architecture. x86-64 is a compatible extension to the 32-bit x86 architecture, implemented by, for example, Intel's own Xeon line and AMD's Opteron line. By 2009, most servers were being shipped with x86-64 processors, and they dominate the low cost desktop and laptop markets which were not initially targeted by Itanium.[10] In an article titled "Intel's Itanium is finally dead: The Itanic sunken by the x86 juggernaut" Techspot declared "Itanium's promise ended up sunken by a lack of legacy 32-bit support and difficulties in working with the architecture for writing and maintaining software" while the dream of a single dominant ISA would be realized by the AMD64 extensions.[11]

History

[edit]Development: 1989–2001

[edit]Inception: 1989–1994

[edit]In 1989, HP started to research an architecture that would exceed the expected limits of the reduced instruction set computer (RISC) architectures caused by the great increase in complexity needed for executing multiple instructions per cycle due to the need for dynamic dependency checking and precise exception handling.[c] HP hired Bob Rau of Cydrome and Josh Fisher of Multiflow, the pioneers of very long instruction word (VLIW) computing. One VLIW instruction word can contain several independent instructions, which can be executed in parallel without having to evaluate them for independence. A compiler must attempt to find valid combinations of instructions that can be executed at the same time, effectively performing the instruction scheduling that conventional superscalar processors must do in hardware at runtime.

HP researchers modified the classic VLIW into a new type of architecture, later named Explicitly Parallel Instruction Computing (EPIC), which differs by: having template bits which show which instructions are independent inside and between the bundles of three instructions, which enables the explicitly parallel execution of multiple bundles and increasing the processors' issue width without the need to recompile; by predication of instructions to reduce the need for branches; and by full interlocking to eliminate the delay slots. In EPIC the assignment of execution units to instructions and the timing of their issuing can be decided by hardware, unlike in the classic VLIW. HP intended to use these features in PA-WideWord, the planned successor to their PA-RISC ISA. EPIC was intended to provide the best balance between the efficient use of silicon area and electricity, and general-purpose flexibility.[13][14] In 1993 HP held an internal competition to design the best (simulated) microarchitectures of a RISC and an EPIC type, led by Jerry Huck and Rajiv Gupta respectively. The EPIC team won, with over double the simulated performance of the RISC competitor.[15]

At the same time Intel was also looking for ways to make better ISAs. In 1989 Intel had launched the i860, which it marketed for workstations, servers, and iPSC and Paragon supercomputers. It differed from other RISCs by being able to switch between the normal single instruction per cycle mode, and a mode where pairs of instructions are explicitly defined as parallel so as to execute them in the same cycle without having to do dependency checking. Another distinguishing feature were the instructions for an exposed floating-point pipeline, that enabled the tripling of throughput compared to the conventional floating-point instructions. Both of these features were left largely unused because compilers didn't support them, a problem that later challenged Itanium too. Without them, i860's parallelism (and thus performance) was no better than other RISCs, so it failed in the market. Itanium would adopt a more flexible form of explicit parallelism than i860 had.[16]

In November 1993 HP approached Intel, seeking collaboration on an innovative future architecture.[17][19] At the time Intel was looking to extend x86 to 64 bits in a processor codenamed P7, which they found challenging.[20] Later Intel claimed that four different design teams had explored 64-bit extensions, but each of them concluded that it was not economically feasible.[21] At the meeting with HP, Intel's engineers were impressed when Jerry Huck and Rajiv Gupta presented the PA-WideWord architecture they had designed to replace PA-RISC. "When we saw WideWord, we saw a lot of things we had only been looking at doing, already in their full glory", said Intel's John Crawford, who in 1994 became the chief architect of Merced, and who had earlier argued against extending the x86 with P7. HP's Gupta recalled: "I looked Albert Yu [Intel's general manager for microprocessors] in the eyes and showed him we could run circles around PowerPC, that we could kill PowerPC, that we could kill the x86."[22] Soon Intel and HP started conducting in-depth technical discussions at an HP office, where each side had six[25] engineers who exchanged and discussed both companies' confidential architectural research. They then decided to use not only PA-WideWord, but also the more experimental HP Labs PlayDoh as the source of their joint future architecture.[12][26] Convinced of the superiority of the new project, in 1994 Intel canceled their existing plans for P7.

In June 1994 Intel and HP announced their joint effort to make a new ISA that would adopt ideas of Wide Word and VLIW. Yu declared: "If I were competitors, I'd be really worried. If you think you have a future, you don't."[22] On P7's future, Intel said the alliance would impact it, but "it is not clear" whether it would "fully encompass the new architecture".[27][28] Later the same month, Intel said that some of the first features of the new architecture would start appearing on Intel chips as early as the P7, but the full version would appear sometime later.[29] In August 1994 EE Times reported that Intel told investors that P7 was being re-evaluated and possibly canceled in favor of the HP processor. Intel immediately issued a clarification, saying that P7 is still being defined, and that HP may contribute to its architecture. Later it was confirmed that the P7 codename had indeed passed to the HP-Intel processor. By early 1996 Intel revealed its new codename, Merced.[30][31]

HP believed that it was no longer cost-effective for individual enterprise systems companies such as itself to develop proprietary microprocessors, so it partnered with Intel in 1994 to develop the IA-64 architecture, derived from EPIC. Intel was willing to undertake the very large development effort on IA-64 in the expectation that the resulting microprocessor would be used by the majority of enterprise systems manufacturers. HP and Intel initiated a large joint development effort with a goal of delivering the first product, Merced, in 1998.[14]

Design and delays: 1994–2001

[edit]Merced was designed by a team of 500, which Intel later admitted was too inexperienced, with many recent college graduates. Crawford (Intel) was the chief architect, while Huck (HP) held the second position. Early in the development HP and Intel had a disagreement where Intel wanted more dedicated hardware for more floating-point instructions. HP prevailed upon the discovery of a floating-point hardware bug in Intel's Pentium. When Merced was floorplanned for the first time in mid-1996, it turned out to be far too large, "this was a lot worse than anything I'd seen before", said Crawford. The designers had to reduce the complexity (and thus performance) of subsystems, including the x86 unit and cutting the L2 cache to 96 KB.[d] Eventually it was agreed that the size target could only be reached by using the 180 nm process instead of the intended 250 nm. Later problems emerged with attempts to speed up the critical paths without disturbing the other circuits' speed. Merced was taped out on 4 July 1999, and in August Intel produced the first complete test chip.[22]

The expectations for Merced waned over time as delays and performance deficiencies emerged, shifting the focus and onus for success onto the HP-led second Itanium design, codenamed McKinley. In July 1997 the switch to the 180 nm process delayed Merced into the second half of 1999.[32] Shortly before the reveal of EPIC at the Microprocessor Forum in October 1997, an analyst of the Microprocessor Report said that Itanium would "not show the competitive performance until 2001. It will take the second version of the chip for the performance to get shown".[33] At the Forum, Intel's Fred Pollack originated the "wait for McKinley" mantra when he said that it would double the Merced's performance and would "knock your socks off",[34][35] while using the same 180 nm process as Merced.[36] Pollack also said that Merced's x86 performance would be lower than the fastest x86 processors, and that x86 would "continue to grow at its historical rates".[34] Intel said that IA-64 won't have much presence in the consumer market for 5 to 10 years.[37]

Later it was reported that HP's motivation when starting to design McKinley in 1996 was to have more control over the project so as to avoid the issues affecting Merced's performance and schedule.[38][39] The design team finalized McKinley's project goals in 1997.[40] In late May 1998 Merced was delayed to mid-2000, and by August 1998 analysts were questioning its commercial viability, given that McKinley would arrive shortly after with double the performance, as delays were causing Merced to turn into simply a development vehicle for the Itanium ecosystem. The "wait for McKinley" narrative was becoming prevalent.[41] The same day it was reported that due to the delays, HP would extend its line of PA-RISC PA-8000 series processors from PA-8500 to as far as PA-8900.[42] In October 1998 HP announced its plans for four more generations of PA-RISC processors, with PA-8900 set to reach 1.2 GHz in 2003.[43]

By March 1999 some analysts expected Merced to ship in volume only in 2001, but the volume was widely expected to be low as most customers would wait for McKinley.[38] In May 1999, two months before Merced's tape-out, an analyst said that failure to tape-out before July would result in another delay.[44] In July 1999, upon reports that the first silicon would be made in late August, analysts predicted a delay to late 2000, and came into agreement that Merced would be used chiefly for debugging and testing the IA-64 software. Linley Gwennap of MPR said of Merced that "at this point, everyone is expecting it's going to be late and slow, and the real advance is going to come from McKinley. What this does is puts a lot more pressure on McKinley and for that team to deliver".[45] By then, Intel had revealed that Merced would be initially priced at $5000.[46] In August 1999 HP advised some of their customers to skip Merced and wait for McKinley.[47] By July 2000 HP told the press that the first Itanium systems would be for niche uses, and that "You're not going to put this stuff near your data center for several years."; HP expected its Itanium systems to outsell the PA-RISC systems only in 2005.[48] The same July Intel told of another delay, due to a stepping change to fix bugs. Now only "pilot systems" would ship that year, while the general availability was pushed to the "first half of 2001". Server makers had largely forgone spending on the R&D for the Merced-based systems, instead using motherboards or whole servers of Intel's design. To foster a wide ecosystem, by mid-2000 Intel had provided 15,000 Itaniums in 5,000 systems to software developers and hardware designers.[49] In March 2001 Intel said Itanium systems would begin shipping to customers in the second quarter, followed by a broader deployment in the second half of the year. By then even Intel publicly acknowledged that many customers would wait for McKinley.[50]

Expectations

[edit]During development, Intel, HP, and industry analysts predicted that IA-64 would dominate first in 64-bit servers and workstations, then expand to the lower-end servers, supplanting Xeon, and finally penetrate into the personal computers, eventually to supplant RISC and complex instruction set computing (CISC) architectures for all general-purpose applications, though not replacing x86 "for the foreseeable future" according to Intel.[53][15][54][55][56][57] In 1997-1998, Intel CEO Andy Grove predicted that Itanium would not come to the desktop computers for four of five years after launch, and said "I don't see Merced appearing on a mainstream desktop inside of a decade".[58][15] In contrast, Itanium was expected to capture 70% of the 64-bit server market in 2002.[59] Already in 1998 Itanium's focus on the high end of the computer market was criticized for making it vulnerable to challengers expanding from the lower-end market segments, but many people in the computer industry feared voicing doubts about Itanium in the fear of Intel's retaliation.[15] Compaq and Silicon Graphics decided to abandon further development of the Alpha and MIPS architectures respectively in favor of migrating to IA-64.[60]

Several groups ported operating systems for the architecture, including Microsoft Windows, OpenVMS, Linux, HP-UX, Solaris,[61][62][63] Tru64 UNIX,[60] and Monterey/64.[64] The latter three were canceled before reaching the market. By 1997, it was apparent that the IA-64 architecture and the compiler were much more difficult to implement than originally thought, and the delivery timeframe of Merced began slipping.[45]

Intel announced the official name of the processor, Itanium, on October 4, 1999.[65] Within hours, the name Itanic had been coined on a Usenet newsgroup, a reference to the RMS Titanic, the "unsinkable" ocean liner that sank on her maiden voyage in 1912.[66] "Itanic" was then used often by The Register,[67] and others,[68][69][70] to imply that the multibillion-dollar investment in Itanium—and the early hype associated with it—would be followed by its relatively quick demise.

Itanium (Merced): 2001

[edit] Itanium processor | |

| General information | |

|---|---|

| Launched | 29 May–June 2001 |

| Discontinued | 10 April 2003[71] |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 733 to 800 MHz |

| FSB speeds | 266 MT/s |

| Cache | |

| L2 cache | 96 KB |

| L3 cache | 2 or 4 MB |

| Physical specifications | |

| Cores |

|

| Socket | |

After having sampled 40,000 chips to the partners, Intel launched Itanium on May 29, 2001, with first OEM systems from HP, IBM and Dell shipping to customers in June.[72][73] By then Itanium's performance was not superior to competing RISC and CISC processors.[74] Itanium competed at the low-end (primarily four-CPU and smaller systems) with servers based on x86 processors, and at the high-end with IBM POWER and Sun Microsystems SPARC processors. Intel repositioned Itanium to focus on the high-end business and HPC computing markets, attempting to duplicate the x86's successful "horizontal" market (i.e., single architecture, multiple systems vendors). The success of this initial processor version was limited to replacing the PA-RISC in HP systems, Alpha in Compaq systems and MIPS in SGI systems, though IBM also delivered a supercomputer based on this processor.[75] POWER and SPARC remained strong, while the 32-bit x86 architecture continued to grow into the enterprise space, building on the economies of scale fueled by its enormous installed base.

Only a few thousand systems using the original Merced Itanium processor were sold, due to relatively poor performance, high cost and limited software availability.[76] Recognizing that the lack of software could be a serious problem for the future, Intel made thousands of these early systems available to independent software vendors (ISVs) to stimulate development. HP and Intel brought the next-generation Itanium 2 processor to the market a year later. Few of the microarchitectural features of Merced would be carried over to all the subsequent Itanium designs, including the 16+16 KB L1 cache size and the 6-wide (two-bundle) instruction decoding.

Itanium 2 (McKinley and Madison): 2002–2006

[edit] Itanium 2 processor | |

| General information | |

|---|---|

| Launched | 8 July 2002 |

| Discontinued | 16 November 2007[80] |

| Designed by | HP and Intel |

| Product code | McKinley, Madison, Deerfield, Madison 9M, Fanwood |

| Performance | |

| Max. CPU clock rate | 900 to 1667 MHz |

| FSB speeds | 400 to 667 MT/s |

| Cache | |

| L2 cache | 256 KB |

| L3 cache | 1.5–9 MB |

| Architecture and classification | |

| Technology node | 180 nm to 130 nm |

| Physical specifications | |

| Cores |

|

| Socket | |

The Itanium 2 processor was released in July 2002, and was marketed for enterprise servers rather than for the whole gamut of high-end computing. The first Itanium 2, code-named McKinley, was jointly developed by HP and Intel, led by the HP team at Fort Collins, Colorado, taping out in December 2000. It relieved many of the performance problems of the original Itanium processor, which were mostly caused by an inefficient memory subsystem by approximately halving the latency and doubling the fill bandwidth of each of the three levels of cache, while expanding the L2 cache from 96 to 256 KB. Floating-point data is excluded from the L1 cache, because the L2 cache's higher bandwidth is more beneficial to typical floating-point applications than low latency. The L3 cache is now integrated on-chip rather than on a separate die, tripling in associativity and doubling in bus width. McKinley also greatly increases the number of possible instruction combinations in a VLIW-bundle and reaches 25% higher frequency, despite having only eight pipeline stages versus Merced's ten.[81][40]

McKinley contains 221 million transistors (of which 25 million are for logic and 181 million for L3 cache), measured 19.5 mm by 21.6 mm (421 mm2) and was fabricated in a 180 nm, bulk CMOS process with six layers of aluminium metallization.[82][83][84] In May 2003 it was disclosed that some McKinley processors can suffer from a critical-path erratum leading to a system's crashing. It can be avoided by lowering the processor frequency to 800 MHz.[85]

In 2003, AMD released the Opteron CPU, which implements its own 64-bit architecture called AMD64. The Opteron gained rapid acceptance in the enterprise server space because it provided an easy upgrade from x86. Under the influence of Microsoft, Intel responded by implementing AMD's x86-64 instruction set architecture instead of IA-64 in its Xeon microprocessors in 2004, resulting in a new industry-wide de facto standard.[60]

In 2003 Intel released a new Itanium 2 family member, codenamed Madison, initially with up to 1.5 GHz frequency and 6 MB of L3 cache. The Madison 9M chip released in November 2004 had 9 MB of L3 cache and frequency up to 1.6 GHz, reaching 1.67 GHz in July 2005. Both chips used a 130 nm process and were the basis of all new Itanium processors until Montecito was released in July 2006, specifically Deerfield being a low wattage Madison, and Fanwood being a version of Madison 9M for lower-end servers with one or two CPU sockets.

In November 2005, the major Itanium server manufacturers joined with Intel and a number of software vendors to form the Itanium Solutions Alliance to promote the architecture and accelerate the software porting effort.[86] The Alliance announced that its members would invest $10 billion in the Itanium Solutions Alliance by the end of the decade.[87]

Itanium 2 9000 and Itanium 9100: 2006 and 2007

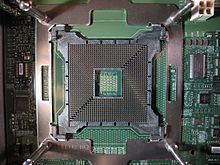

[edit] Intel Itanium 2 9000 (heat spreader removed) | |

| General information | |

|---|---|

| Launched | 18 July 2006 |

| Discontinued | 26 August 2011[88] |

| Product code | Montecito, Montvale |

| Performance | |

| Max. CPU clock rate | 1.4 GHz to 1.67 GHz |

| FSB speeds | 400 to 667 MT/s |

| Cache | |

| L2 cache | 256 KB (D) + 1 MB (I) |

| L3 cache | 6–24 MB |

| Architecture and classification | |

| Technology node | 90 nm |

| Physical specifications | |

| Cores |

|

| Socket | |

In early 2003, due to the success of IBM's dual-core POWER4, Intel announced that the first 90 nm Itanium processor, codenamed Montecito, would be delayed to 2005 so as to change it into a dual-core, thus merging it with the Chivano project.[89][90] In September 2004 Intel demonstrated a working Montecito system, and claimed that the inclusion of hyper-threading increases Montecito's performance by 10-20% and that its frequency could reach 2 GHz.[91][92] After a delay to "mid-2006" and reduction of the frequency to 1.6 GHz,[93] on July 18 Intel delivered Montecito (marketed as the Itanium 2 9000 series), a dual-core processor with a switch-on-event multithreading and split 256 KB + 1 MB L2 caches that roughly doubled the performance and decreased the energy consumption by about 20 percent.[94] At 596 mm² die size and 1.72 billion transistors it was the largest microprocessor at the time. It was supposed to feature Foxton Technology, a very sophisticated frequency regulator, which failed to pass validation and was thus not enabled for customers.

Intel released the Itanium 9100 series, codenamed Montvale, in November 2007, retiring the "Itanium 2" brand.[95] Originally intended to use the 65 nm process,[96] it was changed into a fix of Montecito, enabling the demand-based switching (like EIST) and up to 667 MT/s front-side bus, which were intended for Montecito, plus a core-level lockstep.[91] Montecito and Montvale were the last Itanium processors in which design Hewlett-Packard's engineering team at Fort Collins had a key role, as the team was subsequently transferred to Intel's ownership.[97]

Itanium 9300 (Tukwila): 2010

[edit]| General information | |

|---|---|

| Launched | 8 February 2010 |

| Discontinued | 2nd quarter of 2014 |

| Performance | |

| Max. CPU clock rate | 1.33 to 1.73 GHz |

| Cache | |

| L2 cache | 256 KB (D) + 512 KB (I) |

| L3 cache | 10–24 MB |

| Architecture and classification | |

| Technology node | 65 nm |

| Physical specifications | |

| Cores |

|

| Socket |

|

| General information | |

|---|---|

| Launched | 8 November 2012 |

| Discontinued | 30 January 2020[98] |

| Product code | Poulson, Kittson |

| Performance | |

| Max. CPU clock rate | 1.73 to 2.67 GHz |

| Cache | |

| L2 cache | 256 KB (D) + 512 KB (I) |

| L3 cache | 20–32 MB |

| Architecture and classification | |

| Technology node | 32 nm |

| Physical specifications | |

| Cores |

|

| Socket |

|

The original code name for the first Itanium with more than two cores was Tanglewood, but it was changed to Tukwila in late 2003 due to trademark issues.[99][100] Intel discussed a "middle-of-the-decade Itanium" to succeed Montecito, achieving ten times the performance of Madison.[101][90] It was being designed by the famed DEC Alpha team and was expected have eight new multithreading-focused cores. Intel claimed "a lot more than two" cores and more than seven times the performance of Madison.[102][103][104] In early 2004 Intel told of "plans to achieve up to double the performance over the Intel Xeon processor family at platform cost parity by 2007".[105] By early 2005 Tukwila was redefined, now having fewer cores but focusing on single-threaded performance and multiprocessor scalability.[106]

In March 2005, Intel disclosed some details of Tukwila, the next Itanium processor after Montvale, to be released in 2007. Tukwila would have four processor cores and would replace the Itanium bus with a new Common System Interface, which would also be used by a new Xeon processor.[107] Tukwila was to have a "common platform architecture" with a Xeon codenamed Whitefield,[96] which was canceled in October 2005,[108] when Intel revised Tukwila's delivery date to late 2008.[109] In May 2009, the schedule for Tukwila, was revised again, with the release to OEMs planned for the first quarter of 2010.[110] The Itanium 9300 series processor, codenamed Tukwila, was released on February 8, 2010, with greater performance and memory capacity.[111]

The device uses a 65 nm process, includes two to four cores, up to 24 MB on-die caches, Hyper-Threading technology and integrated memory controllers. It implements double-device data correction, which helps to fix memory errors. Tukwila also implements Intel QuickPath Interconnect (QPI) to replace the Itanium bus-based architecture. It has a peak interprocessor bandwidth of 96 GB/s and a peak memory bandwidth of 34 GB/s. With QuickPath, the processor has integrated memory controllers and interfaces the memory directly, using QPI interfaces to directly connect to other processors and I/O hubs. QuickPath is also used on Intel x86-64 processors using the Nehalem microarchitecture, which possibly enabled Tukwila and Nehalem to use the same chipsets.[112] Tukwila incorporates two memory controllers, each of which has two links to Scalable Memory Buffers, which in turn support multiple DDR3 DIMMs,[113] much like the Nehalem-based Xeon processor code-named Beckton.[114]

HP vs. Oracle

[edit]During the 2012 Hewlett-Packard Co. v. Oracle Corp. support lawsuit, court documents unsealed by a Santa Clara County Court judge revealed that in 2008, Hewlett-Packard had paid Intel around $440 million to keep producing and updating Itanium microprocessors from 2009 to 2014. In 2010, the two companies signed another $250 million deal, which obliged Intel to continue making Itanium CPUs for HP's machines until 2017. Under the terms of the agreements, HP had to pay for chips it gets from Intel, while Intel launches Tukwila, Poulson, Kittson, and Kittson+ chips in a bid to gradually boost performance of the platform.[115][116]

Itanium 9500 (Poulson): 2012

[edit]Intel first mentioned Poulson on March 1, 2005, at the Spring IDF.[117] In June 2007 Intel said that Poulson would use a 32 nm process technology, skipping the 45 nm process.[118] This was necessary for catching up after Itanium's delays left it at 90 nm competing against 65 nm and 45 nm processors.

At ISSCC 2011, Intel presented a paper called "A 32nm 3.1 Billion Transistor 12-Wide-Issue Itanium Processor for Mission Critical Servers."[119][120] Analyst David Kanter speculated that Poulson would use a new microarchitecture, with a more advanced form of multithreading that uses up to two threads, to improve performance for single threaded and multithreaded workloads.[121] Some information was also released at the Hot Chips conference.[122][123]

Information presented improvements in multithreading, resiliency improvements (Intel Instruction Replay RAS) and few new instructions (thread priority, integer instruction, cache prefetching, and data access hints).

Poulson was released on November 8, 2012, as the Itanium 9500 series processor. It is the follow-on processor to Tukwila. It features eight cores and has a 12-wide issue architecture, multithreading enhancements, and new instructions to take advantage of parallelism, especially in virtualization.[112][124][125] The Poulson L3 cache size is 32 MB and common for all cores, not divided like previously. L2 cache size is 6 MB, 512 I KB, 256 D KB per core.[119] Die size is 544 mm², less than its predecessor Tukwila (698.75 mm²).[126][127]

Intel's Product Change Notification (PCN) 111456-01 lists four models of Itanium 9500 series CPU, which was later removed in a revised document.[128] The parts were later listed in Intel's Material Declaration Data Sheets (MDDS) database.[129] Intel later posted Itanium 9500 reference manual.[130]

The models are the following:[128][131]

Processor number Frequency Cache 9520 1.73 GHz 20MB 9540 2.13 GHz 24MB 9550 2.40 GHz 32MB 9560 2.53 GHz 32MB

Itanium 9700 (Kittson): 2017

[edit]Intel had committed to at least one more generation after Poulson, first mentioning Kittson on 14 June 2007.[118] Kittson was supposed to be on a 22 nm process and use the same LGA2011 socket and platform as Xeons.[132][133][134] On 31 January 2013 Intel issued an update to their plans for Kittson: it would have the same LGA1248 socket and 32 nm process as Poulson, thus effectively halting any further development of Itanium processors.[135]

In April 2015, Intel, although it had not yet confirmed formal specifications, did confirm that it continued to work on the project.[136] Meanwhile, the aggressively multicore Xeon E7 platform displaced Itanium-based solutions in the Intel roadmap.[137] Even Hewlett-Packard, the main proponent and customer for Itanium, began selling x86-based Superdome and NonStop servers, and started to treat the Itanium-based versions as legacy products.[138][139]

Intel officially launched the Itanium 9700 series processor family on May 11, 2017.[140][8] Kittson has no microarchitecture improvements over Poulson; despite nominally having a different stepping, it is functionally identical with the 9500 series, even having exactly the same bugs, the only difference being the 133 MHz higher frequency of 9760 and 9750 over 9560 and 9550 respectively.[141][142]

Intel announced that the 9700 series would be the last Itanium chips produced.[7][8]

The models are:[143]

Processor number Cores Threads Frequency Cache 9720 4 8 1.73 GHz 20 MB 9740 8 16 2.13 GHz 24 MB 9750 4 8 2.53 GHz 32 MB 9760 8 16 2.66 GHz 32 MB

Market share

[edit]Compared to its Xeon family of server processors, Itanium was never a high-volume product for Intel. Intel does not release production numbers, but one industry analyst estimated that the production rate was 200,000 processors per year in 2007.[144]

According to Gartner Inc., the total number of Itanium servers (not processors) sold by all vendors in 2007, was about 55,000 (It is unclear whether clustered servers counted as a single server or not.). This compares with 417,000 RISC servers (spread across all RISC vendors) and 8.4 million x86 servers. IDC reports that a total of 184,000 Itanium-based systems were sold from 2001 through 2007. For the combined POWER/SPARC/Itanium systems market, IDC reports that POWER captured 42% of revenue and SPARC captured 32%, while Itanium-based system revenue reached 26% in the second quarter of 2008.[145] According to an IDC analyst, in 2007, HP accounted for perhaps 80% of Itanium systems revenue.[94] According to Gartner, in 2008, HP accounted for 95% of Itanium sales.[146] HP's Itanium system sales were at an annual rate of $4.4Bn at the end of 2008, and declined to $3.5Bn by the end of 2009,[10] compared to a 35% decline in UNIX system revenue for Sun and an 11% drop for IBM, with an x86-64 server revenue increase of 14% during this period.

In December 2012, IDC released a research report stating that Itanium server shipments would remain flat through 2016, with annual shipment of 26,000 systems (a decline of over 50% compared to shipments in 2008).[147]

Hardware support

[edit]Systems

[edit]| Company | Last product | |||

|---|---|---|---|---|

| name | from | to | name | CPUs |

| HP/HPE | 2001 | 2021 | Integrity | 1–256 |

| Compaq | 2001 | 2002 | ProLiant 590 | 1–4 |

| IBM | 2001 | 2005 | System x455 | 1–16 |

| Dell | 2001 | PowerEdge 7250 | 1–4 | |

| Hitachi | 2001 | 2008 | BladeSymphony 1000 |

1–8 |

| Unisys | 2002 | 2009 | ES7000/one | 1–32 |

| SGI | 2001 | 2011 | Altix 4000 | 1–2048 |

| Fujitsu | 2005 | PRIMEQUEST | 1–32 | |

| Bull | 2002 | pre-2015 | NovaScale 9410 | 1–32 |

| NEC | 2002 | 2012 | nx7700i | 1–256 |

| Inspur | 2010 | pre-2015 | TS10000 | 2–1024 |

| Huawei | 2012 | pre-2015 | ? | ? |

By 2006, HP manufactured at least 80% of all Itanium systems, and sold 7,200 in the first quarter of 2006.[148] The bulk of systems sold were enterprise servers and machines for large-scale technical computing, with an average selling price per system in excess of US$200,000. A typical system used eight or more Itanium processors.

By 2012, only a few manufacturers offered Itanium systems, including HP, Bull, NEC, Inspur and Huawei. In addition, Intel offered a chassis that could be used by system integrators to build Itanium systems.[149]

By 2015, only HP supplied Itanium-based systems.[136] When HP split in late 2015, Itanium systems (branded as Integrity)[150] were handled by Hewlett Packard Enterprise (HPE), with a major update in 2017 (Integrity i6, and HP-UX 11i v3 Update 16). HPE also supports a few other operating systems, including Windows up to Server 2008 R2, Linux, OpenVMS and NonStop. Itanium is not affected by Spectre or Meltdown.[151]

Chipsets

[edit]Prior to the 9300-series (Tukwila), chipsets were needed to connect to the main memory and I/O devices, as the front-side bus to the chipset was the sole operational connection to the processor.[e] Two generations of buses existed: the original Itanium processor system bus (a.k.a. Merced bus) had a 64 bit data width and 133 MHz clock with DDR (266 MT/s), being soon superseded by the 128-bit 200 MHz DDR (400 MT/s) Itanium 2 processor system bus (a.k.a. McKinley bus), which later reached 533 and 667 MT/s. Up to four CPUs per single bus could be used, but prior to the 9000-series the bus speeds of over 400 MT/s were limited to up to two processors per bus.[152][153] As no Itanium chipset could connect to more than four sockets, high-end servers needed multiple interconnected chipsets.

The "Tukwila" Itanium processor model had been designed to share a common chipset with the Intel Xeon processor EX (Intel's Xeon processor designed for four processor and larger servers). The goal was to streamline system development and reduce costs for server OEMs, many of which develop both Itanium- and Xeon-based servers. However, in 2013, this goal was pushed back to be "evaluated for future implementation opportunities".[154]

In the times before on-chip memory controllers and QPI, enterprise server manufacturers differentiated their systems by designing and developing chipsets that interface the processor to memory, interconnections, and peripheral controllers. "Enterprise server" referred to the then-lucrative market segment of high-end servers with high reliability, availability and serviceability and typically 16+ processor sockets, justifying their pricing by having a custom system-level architecture with their own chipsets at its heart, with capabilities far beyond what two-socket "commodity servers" could offer. Development of a chipset costs tens of millions of dollars and so represented a major commitment to the use of Itanium.

Neither Intel nor IBM would develop Itanium 2 chipsets to support newer technologies such as DDR2 or PCI Express.[155] Before "Tukwila" moved away from the FSB, chipsets supporting such technologies were manufactured by all Itanium server vendors, such as HP, Fujitsu, SGI, NEC, and Hitachi.

Intel

[edit]The first generation of Itanium received no vendor-specific chipsets, only Intel's 460GX consisting of ten distinct chips. It supported up to four CPUs and 64 GB of memory at 4.2 GB/s, which is twice the system bus's bandwidth. Addresses and data were handled by two different chips. 460GX had an AGP X4 graphics bus, two 64-bit 66 MHz PCI buses and configurable 33 MHz dual 32-bit or single 64-bit PCI bus(es).[156]

There were many custom chipset designs for Itanium 2, but many smaller vendors chose to use Intel's E8870 chipset. It supports 128 GB of DDR SDRAM at 6.4 GB/s. It was originally designed for Rambus RDRAM serial memory, but when RDRAM failed, Intel added four DDR SDRAM-to-RDRAM converter chips to the chipset.[157] When Intel had previously made such a converter for Pentium III chipsets 820 and 840, it drastically cut performance.[158][159] E8870 provides eight 133 MHz PCI-X buses (4.2 GB/s total because of bottlenecks) and a ICH4 hub with six USB 2.0 ports. Two E8870 can be linked together by two E8870SP Scalability Port Switches, each containing a 1MB (~200,000 cache lines) snoop filter, to create an 8-socket system with double the memory and PCI-X capacity, but still only one ICH4. Further expansion to 16 sockets was planned.[160][161][162] In 2004 Intel revealed plans for its next Itanium chipset, codenamed Bayshore, to support PCI-e and DDR2 memory, but canceled it the same year.[163][155]

Hewlett-Packard

[edit]HP has designed four different chipsets for Itanium 2: zx1, sx1000, zx2 and sx2000. All support 4 sockets per chipset, but sx1000 and sx2000 support interconnection of up to 16 chipsets to create up to a 64 socket system. As it was developed in collaboration with Itanium 2's development, booting the first Itanium 2 in February 2001,[164] zx1 became the first Itanium 2 chipset available and later in 2004 also the first to support 533 MT/s FSB. In its basic two-chip version it directly provides four channels of DDR-266 memory, giving 8.5 GB/s of bandwidth and 32 GB of capacity (though 12 DIMM slots).[165] In versions with memory expander boards memory bandwidth reaches 12.8 GB/s, while the maximum capacity for the initial two-board 48 DIMM expanders was 96 GB, and the later single-board 32 DIMM expander up to 128 GB. The memory latency increases by 25 nanoseconds from 80 ns due to the expanders. Eight independent links went to the PCI-X and other peripheral devices (e.g. AGP in workstations), totaling 4 GB/s.[166][167]

HP's first high-end Itanium chipset was sx1000, launched in mid-2003 with the Integrity Superdome flagship server. It has two independent front-side buses, each bus supporting two sockets, giving 12.8 GB/s of combined bandwidth from the processors to the chipset. It has four links to data-only memory buffers and supports 64 GB of HP-designed 125 MHz memory at 16 GB/s. The above components form a system board called a cell. Two cells can be directly connected together to create an 8-socket glueless system. To connect four cells together, a pair of 8-ported crossbar switches is needed (adding 64 ns to inter-cell memory accesses), while four such pairs of crossbar switches are needed for the top-end system of 16 cells (64 sockets), giving 32 GB/s of bisection bandwidth. Cells maintain cache coherence through in-memory directories, which causes the minimum memory latency to be 241 ns. The latency to the most remote (NUMA) memory is 463 ns. The per-cell bandwidth to the I/O subsystems is 2 GB/s, despite the presence of 8 GB/s worth of PCI-X buses in each I/O subsystem.[168][169][170]

HP launched sx2000 in March 2006 to succeed sx1000. Its two FSBs operate at 533 MT/s. It supports up to 128 GB of memory at 17 GB/s. The memory is of HP's custom design, using the DDR2 protocol, but twice as tall as the standard modules and with redundant address and control signal contacts. For the inter-chipset communication, 25.5 GB/s is available on each sx2000 through its three serial links that can connect to a set of three independent crossbars, which connect to other cells or up to 3 other sets of 3 crossbars. The multi-cell configurations are the same as with sx1000, except the parallelism of the sets of crossbars has been increased from 2 to 3. The maximum configuration of 64 sockets has 72 GB/s of sustainable bisection bandwidth. The chipset's connection to its I/O module is now serial with an 8.5 GB/s peak and 5.5 GB/s sustained bandwidth, the I/O module having either 12 PCI-X buses at up to 266 MHz, or 6 PCI-X buses and 6 PCIe 1.1 ×8 slots. It is the last chipset to support HP's PA-RISC processors (PA-8900).[171]

HP launched the first zx2-based servers in September 2006. zx2 can operate the FSB at 667 MT/s with two CPUs or 533 MT/s with four CPUs. It connects to the DDR2 memory either directly, supporting 32 GB at up to 14.2 GB/s, or through expander boards, supporting up to 384 GB at 17 GB/s. The minimum open-page latency is 60 to 78 ns. 9.8 GB/s are available through eight independent links to the I/O adapters, which can include PCIe ×8 or 266 MHz PCI-X.[172][173]

Others

[edit]In May 2003, IBM launched the XA-64 chipset for Itanium 2. It used many of the same technologies as the first two generations of XA-32 chipsets for Xeon, but by the time of the third gen XA-32 IBM had decided to discontinue its Itanium products. XA-64 supported 56 GB of DDR SDRAM in 28 slots at 6.4 GB/s, though due to bottlenecks only 3.2 GB/s could go to the CPU and other 2 GB/s to devices for a 5.2 GB/s total. The CPU's memory bottleneck was mitigated by an off-chip 64 MB DRAM L4 cache, which also worked as a snoop filter in multi-chipset systems. The combined bandwidth of the four PCI-X buses and other I/O is bottlenecked to 2 GB/s per chipset. Two or four chipsets can be connected to make an 8 or 16 socket system.[174]

SGI's Altix supercomputers and servers used the SHUB (Super-Hub) chipset, which supports two Itanium 2 sockets. The initial version used DDR memory through four buses for up to 12.8 GB/s bandwidth, and up to 32 GB of capacity across 16 slots. A 2.4 GB/s XIO channel connected to a module with up to six 64-bit 133 MHz PCI-X buses. SHUBs can be interconnected by the dual 6.4 GB/s NUMAlink4 link planes to create a 512-socket cache-coherent single-image system. A cache for the in-memory coherence directory saves memory bandwidth and reduces latency. The latency to the local memory is 132 ns, and each crossing of a NUMAlink4 router adds 50 ns. I/O modules with four 133 MHz PCI-X buses can connect directly to the NUMAlink4 network.[175][176][177][178] SGI's second-generation SHUB 2.0 chipset supported up to 48 GB of DDR2 memory, 667 MT/s FSB, and could connect to I/O modules providing PCI Express.[179][180] It supports only four local threads, so when having two dual-core CPUs per chipset, Hyper-Threading must be disabled.[181]

Software support

[edit]Unix

[edit]- HP-UX 11 (supported until 2025)

BSD

[edit]- NetBSD (a tier II port[182] that "is a work-in-progress effort to port NetBSD to the Itanium family of processors. Currently no formal release is available."[183])

- FreeBSD (unsupported since 31 October 2018)

Linux

[edit]The Trillian Project was an effort by an industry consortium to port the Linux kernel to the Itanium processor. The project started in May 1999 with the goal of releasing the distribution in time for the initial release of Itanium, then scheduled for early 2000.[184] By the end of 1999, the project included Caldera Systems, CERN, Cygnus Solutions, Hewlett-Packard, IBM, Intel, Red Hat, SGI, SuSE, TurboLinux and VA Linux Systems.[185] The project released the resulting code in February 2000.[184] The code then became part of the mainline Linux kernel more than a year before the release of the first Itanium processor. The Trillian project was able to do this for two reasons:

- the free and open source GCC compiler had already been enhanced to support the Itanium architecture.

- a free and open source simulator had been developed to simulate an Itanium processor on an existing computer.[186]

After the successful completion of Project Trillian, the resulting Linux kernel was used by all of the manufacturers of Itanium systems (HP, IBM, Dell, SGI, Fujitsu, Unisys, Hitachi, and Groupe Bull). With the notable exception of HP, Linux is either the primary OS or the only OS the manufacturer supports for Itanium. Ongoing free and open source software support for Linux on Itanium subsequently coalesced at Gelato.

Distribution support

[edit]In 2005, Fedora Linux started adding support for Itanium[187] and Novell added support for SUSE Linux.[188] In 2007, CentOS added support for Itanium in a new release.[189]

- Gentoo Linux[190] (releases before August 2024)[191]

- Debian (official support was dropped in Debian 8; unofficial support available through Debian Ports until June 2024[192])

- Red Hat Enterprise Linux (unsupported since RHEL 6, had support in RHEL 5 until 2017, which supported other platforms until November 30, 2020)

- SUSE Linux 11 (supported until 2019, for other platforms SUSE 11 was supported until 2022).

Deprecation

[edit]In 2009, Red Hat dropped Itanium support in Enterprise Linux 6.[193] Ubuntu 10.10 dropped support for Itanium.[194] In 2021, Linus Torvalds marked the Itanium code as orphaned. Torvalds said:

"HPE no longer accepts orders for new Itanium hardware, and Intel stopped accepting orders a year ago. While intel is still officially shipping chips until July 29, 2021, it's unlikely that any such orders actually exist. It's dead, Jim."[195][196]

Support for Itanium was removed in Linux 6.7.[197][198]

Microsoft Windows

[edit]- Windows XP 64-Bit Edition (unsupported since June 30, 2005)

- Windows Server 2003 (unsupported since July 14, 2015)

- Windows Server 2008 (unsupported since January 14, 2020, paid Extended Security Updates not available on Itanium)

- Windows Server 2008 R2 (unsupported since January 14, 2020, paid Extended Security Updates not available on Itanium; last Windows version to support Itanium processors)

OpenVMS

[edit]In 2001, Compaq announced that OpenVMS would be ported to the Itanium architecture.[199] This led to the creation of the V8.x releases of OpenVMS, which support both Itanium-based HPE Integrity Servers and DEC Alpha hardware.[200] Since the Itanium porting effort began, ownership of OpenVMS transferred from Compaq to HP in 2001, and then to VMS Software Inc. (VSI) in 2014.[201] Noteworthy releases include:

- V8.0 (2003) - First pre-production release of OpenVMS on Itanium available outside HP.[200]

- V8.2 (2005) - First production-grade release of OpenVMS on Itanium.[200]

- V8.4 (2010) - Final release of OpenVMS supported by HP. Support ended on December 31, 2020.[202]

- V8.4-2L3 (2021) - Final release of OpenVMS on Itanium supported by VSI. Support ends on December 31, 2028.[203]

Support for Itanium has been dropped in the V9.x releases of OpenVMS, which run on x86-64 only.[203]

NonStop OS

[edit]NonStop OS was ported from MIPS-based hardware to Itanium in 2005.[204] NonStop OS was later ported to x86-64 in 2015. Sales of Itanium-based NonStop hardware ended in 2020, with support ending in 2025.[205][206]

Compiler

[edit]GNU Compiler Collection deprecated support for IA-64 in GCC 10, after Intel announced the planned phase-out of this ISA.[207] LLVM (Clang) dropped Itanium support in version 2.6.[208]

Virtualization and emulation

[edit]HP sells a virtualization technology for Itanium called Integrity Virtual Machines.

Emulation is a technique that allows a computer to execute binary code that was compiled for a different type of computer. Before IBM's acquisition of QuickTransit in 2009, application binary software for IRIX/MIPS and Solaris/SPARC could run via type of emulation called "dynamic binary translation" on Linux/Itanium. Similarly, HP implemented a method to execute PA-RISC/HP-UX on the Itanium/HP-UX via emulation, to simplify migration of its PA-RISC customers to the radically different Itanium instruction set. Itanium processors can also run the mainframe environment GCOS from Groupe Bull and several x86 operating systems via instruction set simulators.

Competition

[edit]

processors in the TOP500 ranking list of supercomputers (1993–2019)

Itanium was aimed at the enterprise server and high-performance computing (HPC) markets. Other enterprise- and HPC-focused processor lines include Oracle's and Fujitsu's SPARC processors and IBM's Power microprocessors. Measured by quantity sold, Itanium's most serious competition came from x86-64 processors including Intel's own Xeon line and AMD's Opteron line. Since 2009, most servers were being shipped with x86-64 processors.[10]

In 2005, Itanium systems accounted for about 14% of HPC systems revenue, but the percentage declined as the industry shifted to x86-64 clusters for this application.[209]

An October 2008 Gartner report on the Tukwila processor stated that "...the future roadmap for Itanium looks as strong as that of any RISC peer like Power or SPARC."[210]

Supercomputers and high-performance computing

[edit]An Itanium-based computer first appeared on the list of the TOP500 supercomputers in November 2001.[75] The best position ever achieved by an Itanium 2 based system in the list was No. 2, achieved in June 2004, when Thunder (Lawrence Livermore National Laboratory) entered the list with an Rmax of 19.94 Teraflops. In November 2004, Columbia entered the list at No. 2 with 51.8 Teraflops, and there was at least one Itanium-based computer in the top 10 from then until June 2007. The peak number of Itanium-based machines on the list occurred in the November 2004 list, at 84 systems (16.8%); by June 2012, this had dropped to one system (0.2%),[211] and no Itanium system remained on the list in November 2012.

Processors

[edit]Released processors

[edit]

The Itanium processors show a progression in capability. Merced was a proof of concept. McKinley dramatically improved the memory hierarchy and allowed Itanium to become reasonably competitive. Madison, with the shift to a 130 nm process, allowed for enough cache space to overcome the major performance bottlenecks. Montecito, with a 90 nm process, allowed for a dual-core implementation and a major improvement in performance per watt. Montvale added three new features: core-level lockstep, demand-based switching and front-side bus frequency of up to 667 MHz.

| Codename | process | Released | Clock | L2 Cache/ core |

L3 Cache/ processor |

Bus | dies/ dev. |

cores/ die |

TDP/ dev. |

Comments |

|---|---|---|---|---|---|---|---|---|---|---|

| Itanium | ||||||||||

| Merced | 180 nm | 2001-05-29 | 733 MHz | 96 KB | 1 MB

2 MB |

266 MHz | 1 | 1 | 116 | 2 or 4 MB off-die L3 cache |

| 800 MHz | 130 | 2 or 4 MB off-die L3 cache | ||||||||

| Itanium 2 | ||||||||||

| McKinley | 180 nm | 2002-07-08 | 900 MHz | 256 KB | 1.5 MB | 400 MHz | 1 | 1 | 90 | HW branchlong |

| 1 GHz | 100 | |||||||||

| 3 MB | | |||||||||

| Madison | 130 nm | 2003-06-30 | 1.3 GHz | 3 MB | 97 | |||||

| 1.4 GHz | 4 MB | 91 | ||||||||

| 1.5 GHz | 6 MB | 107 | ||||||||

| 2003-09-08 | 1.4 GHz | 1.5 MB | 91 | |||||||

| 2004-04-13 | 3 MB | |||||||||

| 1.6 GHz | 99 | |||||||||

| Deerfield | 2003-09-08 | 1.0 GHz | 1.5 MB | 55 | Low voltage | |||||

| Hondo[212] | 2004-06 | 1.1 GHz | 4 MB | 2 | 1 | 170 | Not a product of Intel, but of HP. 32 MB L4 | |||

| Fanwood | 2004-11-08 | 1.3 GHz | 3 MB | 1 | 1 | 62 | Low voltage | |||

| 1.6 GHz | 99 | |||||||||

| 533 MHz | ||||||||||

| Madison 9M | 1.5 GHz | 4 MB | 400 MHz | 122 | ||||||

| 1.6 GHz | 6 MB | |||||||||

| 9 MB | ||||||||||

| 2005-07-05 | 1.67 GHz | 6 MB | 667 MHz | |||||||

| 9 MB | ||||||||||

| Itanium 2 9000 series | ||||||||||

| Montecito | 90 nm | 2006-07-18 | 1.4– 1.6 GHz |

256 KB (D)+ 1 MB (I) |

6–24 MB | 400– 533 MHz |

1 | 2 | 75–104 | Virtualization, Multithread, no HW IA-32 |

| Itanium 9100 series | ||||||||||

| Montvale | 90 nm | 2007-10-31 | 1.42– 1.66 GHz |

256 KB (D)+ 1 MB (I) |

8–24 MB | 400– 667 MHz |

1 | 1–2 | 75–104 | Core-level lockstep, demand-based switching |

| Itanium 9300 series | ||||||||||

| Tukwila | 65 nm | 2010-02-08 | 1.33– 1.73 GHz |

256 KB (D)+ 512 KB (I) |

10–24 MB | QPI with 4.8 GT/s |

1 | 2–4 | 130–185 | A new point-to-point processor interconnect, the QPI, replacing the FSB. Turbo Boost |

| Itanium 9500 series | ||||||||||

| Poulson | 32 nm | 2012-11-08 [213] |

1.73– 2.53 GHz |

256 KB (D)+ 512 KB (I) |

20–32 MB | QPI with 6.4 GT/s |

1 | 4–8 | 130–170 | Doubled issue width (from 6 to 12 instructions per cycle), Instruction Replay technology, Dual-domain hyperthreading[214][124][215] |

| Itanium 9700 series | ||||||||||

| Kittson | 32 nm | 2017-05-11 [8] |

1.73– 2.66 GHz |

256 KB (D)+ 512 KB (I) |

20–32 MB | QPI with 6.4 GT/s |

1 | 4–8 | 130–170 | No architectural improvements over Poulson, 5 % higher clock for the top model |

| Codename | process | Released | Clock | L2 Cache/ core |

L3 Cache/ processor |

Bus | dies/ dev. |

cores/ die |

watts/ dev. |

Comments |

| List of Intel Itanium processors | ||||||||||

Market reception

[edit]High-end server market

[edit]

When first released in 2001, Itanium's performance was disappointing compared to better-established RISC and CISC processors.[56][57] Emulation to run existing x86 applications and operating systems was particularly poor, with one benchmark in 2001 reporting that it was equivalent at best to a 100 MHz Pentium in this mode (1.1 GHz Pentiums were on the market at that time).[216] Itanium failed to make significant inroads against IA-32 or RISC, and suffered further following the arrival of x86-64 systems which offered greater compatibility with older x86 applications.

In a 2009 article on the history of the processor — "How the Itanium Killed the Computer Industry" — journalist John C. Dvorak reported "This continues to be one of the great fiascos of the last 50 years".[217] Tech columnist Ashlee Vance commented that the delays and underperformance "turned the product into a joke in the chip industry".[146] In an interview, Donald Knuth said "The Itanium approach...was supposed to be so terrific—until it turned out that the wished-for compilers were basically impossible to write."[218]

Both Red Hat and Microsoft announced plans to drop Itanium support in their operating systems due to lack of market interest;[219][220] however, other Linux distributions such as Gentoo and Debian remain available for Itanium. On March 22, 2011, Oracle Corporation announced that it would no longer develop new products for HP-UX on Itanium, although it would continue to provide support for existing products.[221] Following this announcement, HP sued Oracle for breach of contract, arguing that Oracle had violated conditions imposed during settlement over Oracle's hiring of former HP CEO Mark Hurd as its co-CEO, requiring the vendor to support Itanium on its software "until such time as HP discontinues the sales of its Itanium-based servers",[222] and that the breach had harmed its business. In 2012, a court ruled in favor of HP, and ordered Oracle to resume its support for Itanium. In June 2016, Hewlett Packard Enterprise (the corporate successor to HP's server business) was awarded $3 billion in damages from the lawsuit.[223][224] Oracle unsuccessfully appealed the decision to the California Court of Appeal in 2021.[225]

A former Intel official reported that the Itanium business had become profitable for Intel in late 2009.[226] By 2009, the chip was almost entirely deployed on servers made by HP, which had over 95% of the Itanium server market share,[146] making the main operating system for Itanium HP-UX. On March 22, 2011, Intel reaffirmed its commitment to Itanium with multiple generations of chips in development and on schedule.[227]

Other markets

[edit]

Although Itanium did attain limited success in the niche market of high-end computing, Intel had originally hoped it would find broader acceptance as a replacement for the original x86 architecture.[228]

AMD chose a different direction, designing the less radical x86-64, a 64-bit extension to the existing x86 architecture, which Microsoft then supported, forcing Intel to introduce the same extensions in its own x86-based processors.[229] These designs can run existing 32-bit applications at native hardware speed, while offering support for 64-bit memory addressing and other enhancements to new applications.[146] This architecture has now become the predominant 64-bit architecture in the desktop and portable market. Although some Itanium-based workstations were initially introduced by companies such as SGI, they are no longer available.

Timeline

[edit]1989

- HP begins investigating EPIC.[14]

1994

- June: HP and Intel announce partnership.[230]

1995

- September: HP, Novell, and SCO announce plans for a "high volume UNIX operating system" to deliver "64-bit networked computing on the HP/Intel architecture".[231]

1996

1997

- June: IDC predicts IA-64 systems sales will reach $38bn/yr by 2001.[51]

- October: Dell announces it will use IA-64.[233]

- December: Intel and Sun announce joint effort to port Solaris to IA-64.[61][62][63]

1998

- March: SCO admits HP/SCO Unix alliance is now dead.

- June: IDC predicts IA-64 systems sales will reach $30bn/yr by 2001.[51]

- June: Intel announces Merced will be delayed, from second half of 1999 to first half of 2000.[234]

- September: IBM announces it will build Merced-based machines.[235]

- October: Project Monterey is formed to create a common UNIX for IA-64.

1999

- February: Project Trillian is formed to port Linux to IA-64.

- August: IDC predicts IA-64 systems sales will reach $25bn/yr by 2002.[51]

- October: Intel announces the Itanium name.

- October: the term Itanic is first used in The Register.[67]

2000

- February: Project Trillian delivers source code.

- June: IDC predicts Itanium systems sales will reach $25bn/yr by 2003.[51]

- July: Sun and Intel drop Solaris-on-Itanium plans.[236]

- August: AMD releases specification for x86-64, a set of 64-bit extensions to Intel's own x86 architecture intended to compete with IA-64. It will eventually market this under the name "AMD64".

2001

- June: IDC predicts Itanium systems sales will reach $15bn/yr by 2004.[51]

- June: Project Monterey dies.

- July: Itanium is released.

- October: IDC predicts Itanium systems sales will reach $12bn/yr by the end of 2004.[51]

- October 25:The final client version of Windows available for IA-64, Windows XP is released.

- November: IBM's 320-processor Titan NOW Cluster at National Center for Supercomputing Applications is listed on the TOP500 list at position #34.[75]

- November: Compaq delays Itanium Product release due to problems with processor.[237]

- December: Gelato is formed.

2002

- March: IDC predicts Itanium systems sales will reach $5bn/yr by end 2004.[51]

- June: Itanium 2 is released.

2003

- April: IDC predicts Itanium systems sales will reach $9bn/yr by end 2007.[51]

- April: AMD releases Opteron, the first processor with x86-64 extensions.

- June: Intel releases the "Madison" Itanium 2.

2004

- February: Intel announces it has been working on its own x86-64 implementation (which it will eventually market under the name "Intel 64").

- June: Intel releases its first processor with x86-64 extensions, a Xeon processor codenamed "Nocona".

- June: Thunder, a system at LLNL with 4096 Itanium 2 processors, is listed on the TOP500 list at position #2.[238]

- November: Columbia, an SGI Altix 3700 with 10160 Itanium 2 processors at NASA Ames Research Center, is listed on the TOP500 list at position #2.[239]

- December: Itanium system sales for 2004 reach $1.4bn.

2005

- January: HP ports OpenVMS to Itanium[240]

- February: IBM server design drops Itanium support.[155][241]

- June: An Itanium 2 sets a record SPECfp2000 result of 2,801 in a Hitachi, Ltd. Computing blade.[242]

- September: Itanium Solutions Alliance is formed.[243]

- September: Dell exits the Itanium business.[244]

- October: Itanium server sales reach $619M/quarter in the third quarter.

- October: Intel announces one-year delays for Montecito, Montvale, and Tukwila.[109]

2006

- January: Itanium Solutions Alliance announces a $10bn collective investment in Itanium by 2010.

- February: IDC predicts Itanium systems sales will reach $6.6bn/yr by 2009.[52]

- July: Intel releases the dual-core "Montecito" Itanium 2 9000 series.[245]

2007

- April: CentOS (RHEL-clone) places Itanium support on hold for the 5.0 release.[246]

- October: Intel releases the "Montvale" Itanium 2 9100 series.

- November: Intel renames the family from Itanium 2 back to Itanium.

2009

- December: Red Hat announces that it is dropping support for Itanium in the next release of its enterprise OS, Red Hat Enterprise Linux 6.[193]

2010

- February: Intel announces the "Tukwila" Itanium 9300 series.[111]

- April: Microsoft announces that Windows Server 2008 R2 will be the final version of Windows Server to support Itanium.[247]

- October: Intel announces new releases of Intel C++ Compiler and Intel Fortran Compiler for x86/x64, while Itanium support is only available in older versions.[248]

2011

- March: Oracle Corporation announces that it will stop developing application software, middleware, and Oracle Linux for the Itanium.[221]

- March: Intel and HP reiterate their support of Itanium.[249][250]

- April: Huawei and Inspur announce that they will develop Itanium servers.[251]

2012

- February: Court papers were released from a case between HP and Oracle Corporation that gave insight to the fact that HP was paying Intel $690 million to keep Itanium on life support.[252]

- SAP discontinues support for Business Objects on Itanium.[253]

- September: In response to a court ruling, Oracle reinstitutes support for Oracle software on Itanium hardware.[254]

2013

- January: Intel cancels Kittson as a 22 nm shrink of Poulson, moving it instead to its 32 nm process.[255]

- November: HP announces that its NonStop servers will start using Intel 64 (x86-64) chips.[256]

2014

- July: VMS Software Inc (VSI) announces that OpenVMS will be ported to x86-64.[257]

- December: HP announces that their next generation of Superdome X and Nonstop X servers would be equipped with Intel Xeon processors, and not Itanium. While HP continues to sell and offer support for the Itanium-based Integrity portfolio, the introduction of a model based entirely on Xeon chips marks the end of an era.[258]

2017

- February: Intel ships test versions of Kittson, the first new Itanium chip since 2012.[259]

- May: Kittson formally ships in volume as the Itanium 9700 series. Intel states that Kittson is the final Itanium generation.[7]

2019

- January: Intel announces Itanium's end of life with additional orders accepted until January 2020 and last shipments no later than July 2021.[1]

2020

- Hewlett Packard Enterprise (HPE) is accepting the last orders for the latest Itanium i6 servers on December 31, 2020.[260]

2021

- February: Linus Torvalds marks the Itanium port of Linux as orphaned. "HPE no longer accepts orders for new Itanium hardware, and Intel stopped accepting orders a year ago. While Intel is still officially shipping chips until July 29, 2021, it's unlikely that any such orders actually exist. It's dead, Jim."[261]

- July 29: The last batch of Itanium processors is shipped by Intel.[150]

2023

- November: Support for Itanium is removed from the Linux kernel source code.[262]

See also

[edit]Notes

[edit]- ^ Itanium was launched on 29 May,[2][3][4][5] but the computers containing it shipped to customers in June.

- ^ Hondo is an HP product, not an Intel product

- ^ The size of the needed dependency-checking circuitry increases quadratically with the issue width.[12][13]

- ^ For comparison the 180nm Pentium III Xeon MP had a 2 MB on-die L2 cache.

- ^ the processor supported TAP (JTAG) and SMBus for debugging and system configuration

References

[edit]- ^ a b c "Select Intel Itanium Processors and Intel Scalable Memory Buffer, PCN 116733-00, Product Discontinuance, End of Life" (PDF). Intel. January 30, 2019. Archived (PDF) from the original on May 22, 2020. Retrieved May 20, 2020.

(January 30, 2020 was the last date for placing an order, all shipped no later than July 29, 2021). - ^ "Intel officially launches 64-bit Itanium chip". Computerworld. 29 May 2001.

- ^ Fordahl, Matthew (30 May 2001). "Intel, HP Launch New Processor". ABC News.

- ^ Bekker, Scott (29 May 2001). "Intel Launches Itanium: OEMs Unveil Systems". RCP Mag.

- ^ Kerridge, Suzanna (18 May 2001). "Intel opens up about forthcoming Itanium family". ZDNet.

- ^ Morgan, Timothy (May 27, 2008). "The Server Biz Enjoys the X64 Upgrade Cycle in Q1". IT Jungle. Archived from the original on March 3, 2016. Retrieved October 29, 2008.

- ^ a b c Davis, Lisa M. (May 11, 2017). "The Evolution of Mission Critical Computing". Intel. Archived from the original on September 8, 2018. Retrieved May 11, 2017.

...the 9700 series will be the last Intel Itanium processor.

- ^ a b c d Shah, Agam (May 11, 2017). "Intel's Itanium, once destined to replace x86 processors in PCs, hits end of line". PC World. Archived from the original on March 15, 2019. Retrieved May 20, 2020.

- ^ Sharwood, Simon (July 30, 2021). "The Register just found 300-odd Itanium CPUs on eBay". The Register. Archived from the original on September 12, 2021. Retrieved September 12, 2021.

- ^ a b c Morgan, Timothy Prickett (February 24, 2010). "Gartner report card gives high marks to x64, blades". The Register. Retrieved November 25, 2022.

- ^ Lee, Matthew (August 2021). "Intel's Itanium is finally dead: The Itanic sunken by the x86 juggernaut". Techspot. Retrieved 26 March 2023.

- ^ a b DeMone, Paul (27 October 1999). "HP's Struggle For Simplicity Ends at Intel". Real World Tech.

- ^ a b Smotherman, Mark. "Understanding EPIC Architectures and Implementations" (PDF). Clemson University. Retrieved 5 June 2022.

- ^ a b c "Inventing Itanium: How HP Labs Helped Create the Next-Generation Chip Architecture". HP Labs. June 2001. Retrieved March 23, 2007.

- ^ a b c d Markoff, John (5 April 1998). "Inside Intel, The Future is Riding on the Merced Chip". The New York Times, republised by The Jerusalem Post.

- ^ DeMone, Paul (25 January 2000). "Intel's History Lesson". Real World Tech.

- ^ a b DeMone, Paul (14 March 2001). "Countdown to IA-64". Real World Tech.

- ^ Smotherman, Mark. "Who are the Computer Architects?". Clemson University. See the sections "Independence architecture" and "Wintel".

- ^ Alpert, Donald (July 2003). "Intel Itanium Processor (Merced)". Alpert was the chief architect of the original P7 and the top engineering manager of Merced[18]

- ^ DeMone, Paul (3 March 2000). "What's Up With Willamette? (Part 1)". Real World Tech.

- ^ Kanellos, Michael (21 February 2003). "Intel takes slow road to 64-bit PC chips". CNET.

- ^ a b c Hamilton, David (28 May 2001). "Intel gambles with Itanium". ZDNet.

- ^ Britt, Russ (1 January 2000). "The birth of a new processor". EDN.

- ^ Smotherman, Mark. "Historical background for EPIC instruction set architectures". Clemson University. Retrieved 3 June 2022.

- ^ [17][23] (The ACM committee with 5 people from each side[24] was probably a different entity.)

- ^ Kathail, Vinod; Schlansker, Michael S.; Rau, B. Ramakrishna. "HPL-PD Architecture Specification: Version 1.1" (PDF). HP Laboratories. Archived from the original (PDF) on 2024-02-04. Retrieved 2023-07-05.

- ^ Hecht, Jeff (18 June 1994). "Technology: Intel opts for simpler, speedier chips". New Scientist.

- ^ Bozman, Jean S. (13 June 1994). "Chip alliance shakes ground". Computerworld. David House had approved the project, but later severely criticized it.

- ^ Babcock, Charles (25 July 1994). "Silicon marriage: HP/Intel venture". Computerworld.

- ^ DeMone, Paul (14 March 2001). "Countdown to IA-64". Real World Tech. Has a typo (P5) in the graphic.

- ^ Crothers, Brooke (29 January 1996). "Intel aims to bring multimedia to the masses". InfoWorld.

- ^ "Merced "Will Be Out Late 1999," Says Hewlett-Packard". Tech Monitor. Computer Business Review. 18 July 1997. Archived from the original on 13 February 2024.

- ^ Kanellos, Michael (6 October 1997). "Intel late to 64-bit computing". CNET. Archived from the original on Jun 27, 2022.

- ^ a b Kanellos, Michael (14 October 1997). "Intel, HP unveil EPIC technology". CNET. Archived from the original on Aug 18, 2022.

- ^ DeMone, Paul (27 October 1999). "HP's Struggle For Simplicity Ends at Intel". Real World Tech. p. 3. Archived from the original on Oct 31, 2023.

- ^ Gwennap, Linley (27 October 1997). "Intel, HP Make EPIC Disclosure" (PDF). Microprocessor Report. Vol. 11, no. 14. Archived (PDF) from the original on Oct 31, 2023.

- ^ Corcoran, Elizabeth (15 October 1997). "Chipmakers unveil works in progress". The Washington Post. Archived from the original on 13 February 2024.

- ^ a b Robertson, Chiyo (17 March 1999). "Merced: Worth the wait? What of McKinley?". ZDNet.

- ^ Matsumoto, Craig (8 October 1998). "Intel outlines road to McKinley processor". EE Times.

- ^ a b "Inside the Intel Itanium 2 Processor: a Hewlett Packard Technical White Paper". 17 July 2002. CiteSeerX 10.1.1.96.8209.

- ^ Kanellos, Michael (6 August 1998). "Is Merced doomed?". CNET.

- ^ "INTEL'S MERCED COULD BE ECLIPSED BY MCKINLEY FOLLOW-ON". Tech Monitor. 6 August 1998.

- ^ Shankland, Stephen; Kanellos, Michael (13 October 1998). "HP has two-pronged chip plan". CNET. Archived from the original on 2000-12-03.

- ^ Gary, Gregory (3 May 1999). "IA 64 Update: Part 1 of 2". EDN.

- ^ a b Shankland, Stephen (8 July 1999). "Intel's Merced chip may slip further". CNET. Archived from the original on 2000-06-05.

- ^ Hamblen, Matt (12 July 1999). "Intel: No Forced March to Merced". Computerworld.

- ^ Shankland, Stephen (19 August 1999). "HP upgrade path bypasses Merced chip". CNET. Archived from the original on 2000-08-19.

- ^ Shankland, Stephen (11 July 2000). "HP moves slowly into world of Intel 64-bit processors". CNET. Archived from the original on 2001-02-10.

- ^ Shankland, Stephen; Kanellos, Michael (July 18, 2000). "Intel pushes back schedule for Itanium chip". CNET. Archived from the original on 2001-04-13.

- ^ Shankland, Stephen (1 March 2001). "Intel draws out Itanium arrival". CNET. Archived from the original on 2001-04-13.

- ^ a b c d e f g h i "Mining Itanium". CNet News. December 7, 2005. Archived from the original on June 11, 2018. Retrieved March 19, 2007.

- ^ a b Shankland, Stephen (February 14, 2006). "Analyst firm offers rosy view of Itanium". CNET News. Archived from the original on June 24, 2016. Retrieved March 20, 2007.

- ^ Halfhill, Tom R. (December 1997). "Beyond Pentium II". Byte. Archived from the original on 2000-03-02.

- ^ Connor, Deni (1 March 1999). "Intel's Merced will coexist with 32-bit chips". Network World.

- ^ Knorr, Eric (10 September 2001). "Upgrading your server: A look at the Itanium". ZDNet.

- ^ a b De Gelas, Johan (November 9, 2005). "Itanium–Is there light at the end of the tunnel?". AnandTech. Archived from the original on May 3, 2012. Retrieved March 23, 2007.

- ^ a b Takahashi, Dean (May 8, 2009). "Exit interview: Retiring Intel chairman Craig Barrett on the industry's unfinished business". VentureBeat. Archived from the original on April 21, 2018. Retrieved May 17, 2009.

- ^ Nash, Kim S. (6 July 1998). "Behind the Merced Mystique". Computerworld.

- ^ Yu, Elleen (25 November 1998). "IA-64 to overtake RISC". ARN. Archived from the original on 29 January 2023. Retrieved 16 August 2022.

- ^ a b c "Itanium: A cautionary tale". Tech News on ZDNet. December 7, 2005. Archived from the original on August 2, 2020. Retrieved January 1, 2019.

- ^ a b Vijayan, Jaikumar (September 1, 1999). "Solaris for IA-64 coming this fall". Computerworld. Archived from the original on January 15, 2000.

- ^ a b Wolfe, Alexander (September 2, 1999). "Core-logic efforts under way for Merced". EE Times. Archived from the original on December 17, 2019. Retrieved December 17, 2019.

- ^ a b "Sun Introduces Solaris Developer Kit for Intel to Speed Development of Applications On Solaris; Award-winning Sun Tools Help ISVs Easily Develop for Solaris on Intel Today". Business Wire. March 10, 1998. Archived from the original on August 5, 2016. Retrieved June 6, 2016.

...developers can quickly develop applications today that will be compatible with and can easily be tuned for Solaris on Merced.

- ^ Shankland, Stephen (September 17, 1999). "Next-generation chip passes key milestone". CNET News.

- ^ Kanellos, Michael (October 4, 1999). "Intel names Merced chip Itanium". CNET. Retrieved April 30, 2007.

- ^ Finstad, Kraig (October 4, 1999). "Re:Itanium". Newsgroup: comp.sys.mac.advocacy. Retrieved May 20, 2020.

- ^ a b Sherriff, Pete (October 28, 1999). "AMD vs Intel – our readers write". The Register. Retrieved November 25, 2022.

- ^ Berlind, David (November 30, 2001). "Interpreting McNealy's lexicon". ZDNet Tech Update. Archived from the original on September 4, 2019. Retrieved March 19, 2007.

- ^ Demerjian, Charlie (July 18, 2006). "Itanic shell game continues". The Inquirer. Archived from the original on March 5, 2016. Retrieved February 27, 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ Morgenson, Gretchen (October 19, 2003). "Fawning Analysts Betray Investors". The New York Times. Archived from the original on October 11, 2012. Retrieved January 1, 2019.

- ^ "Product Change Notification" (PDF). Intel. Archived from the original (PDF) on 2004-07-19.

- ^ Niccolai, James (IDG News Service) (29 May 2001). "Intel officially launches 64-bit Itanium chip". Computerworld. Retrieved 30 March 2022.

- ^ "Server makers tout Itanium models". ZDNet. Retrieved 30 March 2022.

- ^ Linley Gwennap (June 4, 2001). "Itanium era dawns". EE Times. Archived from the original on December 17, 2019. Retrieved December 17, 2019.

- ^ a b c "Titan Cluster Itanium 800 MHz". TOP500 web site. Archived from the original on September 25, 2006. Retrieved May 16, 2007.

- ^ Michael Kanellos (December 11, 2001). "Itanium sales off to a slow start". CNET News. Retrieved July 4, 2023.

- ^ "Product Change Notification" (PDF). Intel. Archived from the original (PDF) on 2004-07-19.

- ^ "Product Change Notification" (PDF). Intel. Archived from the original (PDF) on 2006-03-13.

- ^ "Product Change Notification" (PDF). Intel.

Warning: forced download. Retrieved 28 April 2022. - ^ McKinley: 16 April 2004[77]

Madison 6M: 28 July 2006[78]

Madison 9M: 16 November 2007[79] - ^ Hammond, Gary; Naffziger, Sam. "Next Generation Itanium™ Processor Overview" (PDF). Archived from the original (PDF) on 6 July 2003.

- ^ Naffzinger, Samuel D.; Colon-Bonet, Glenn T.; Fischer, Timothy; Riedlinger, Reid; Sullivan, Thomas J.; Grutkowski, Tom (November 2002). "The implementation of the Itanium 2 microprocessor" (PDF). IEEE Journal of Solid-State Circuits. 37 (11): 1448–1460. Bibcode:2002IJSSC..37.1448N. doi:10.1109/JSSC.2002.803943. Archived from the original (PDF) on 2003-03-22.

- ^ Soltis, Don; Gibson, Mark. "Itanium® 2 Processor Microarchitecture Overview" (PDF). Hot Chips. Archived from the original (PDF) on 31 May 2005.