HP 2100

The HP 2100 is a series of 16-bit minicomputers that were produced by Hewlett-Packard (HP) from the mid-1960s to early 1990s. Tens of thousands of machines in the series were sold over its 25-year lifetime, making HP the fourth-largest minicomputer vendor during the 1970s.

The design started at Data Systems Inc (DSI), and was originally known as the DSI-1000. HP purchased the company in 1964 and merged it into their Dymec division. The original model, the 2116A built using integrated circuits and magnetic-core memory, was released in 1966. Over the next four years, models A through C were released with different types of memory and expansion, as well as the cost-reduced 2115 and 2114 models. All of these models were replaced by the HP 2100 series in 1971,[1] and then again as the 21MX series in 1974 when the magnetic-core memory was replaced with semiconductor memory.[2]

All of these models were also packaged as the HP 2000 series, combining a 2100-series machine with optional components in order to run the BASIC programming language in a multi-user time sharing fashion. HP Time-Shared BASIC was popular in the 1970s, and many early BASIC programs were written on or for the platform, most notably the seminal Star Trek that was popular during the early home computer era. The People's Computer Company published their programs in HP 2000 format.

The introduction of the HP 3000 in 1974 provided high-end competition to the 2100 series; the entire line was renamed as the HP 1000 in 1977 and positioned as real-time computers. A greatly redesigned version was introduced in 1979 as the 1000 L-Series, using CMOS large scale integration chips and introducing a desk-side tower case model. This was the first version to break backward compatibility with previous 2100-series expansion cards. The final upgrade was the A-series, with new processors capable of more than 1 MIPS performance,[3] with the final A990 released in 1990.[4]

History

[edit]Origins

[edit]HP formed Dynac in 1956 to act as a development shop for projects the main company would not normally undertake. Their original logo was simply the HP logo turned upside down, forming something approximating "dy" and thus inspiring the name. Learning that Westinghouse owned a trademark on that name, in 1958 they changed it to Dymec. The company was brought in-house in 1959 to become the Dymec Division, and in November 1967 was renamed the Palo Alto Division.[5]

Dymec originally made a variety of products for the HP family, but over time became primarily an integrator, building test equipment and similar systems that were used by HP. In 1964, Kay Magleby and Paul Stoft began experimenting with the use of PDP-5 and PDP-8 computers to act as controllers for their complex test systems, but they felt the machines would require changes to truly suit their needs. At the time, Digital Equipment Corporation (DEC) was still a small company and a takeover target. David Packard found Ken Olsen too difficult to deal with, and such plans went nowhere.[5]

Looking for another design they could purchase, Packard was led to the five-person Data Systems, Inc. (DSI) of Detroit. DSI was owned by Union Carbide, and when Packard asked how it was that Union Carbide came to own a computer company, HP Labs manager Barney Oliver replied, "We didn't demand an answer to that question." Bill Hewlett initially refused to consider the development of a "minicomputer", but when Packard reframed it as an "instrument controller" the deal was approved.[5]

DSI was purchased in 1964 and initially set up at Dymec with four of the original five employees of DSI and a number of other employees coming from HP's instrumentation divisions.[5][6] The computer group later moved to its own offices in Cupertino, California, in a building purchased from Varian Associates, becoming the Cupertino Division.[5]

First models

[edit]

Led by Magleby, the new division completed the design as the 2116A, which was demonstrated 7–10 November 1966 at the Joint Computer Conference in San Francisco.[7][8] It was one of the earliest 16-bit minis to hit the market, but at the time it was more notable as "an unusual new instrumentation computer" with a highly expandable design and real-time support. The system featured an oversized cabinet that held up to 16 expansion cards, or could be further expanded to 48 cards with an external expansion cage.

The system launched with 20 different instrumentation cards, including "counters, nuclear scalers, electronic thermometers, digital voltmeters, ac/ohms converters, data amplifiers, and input scanners." An additional set added input/output devices like tape drives, printers, punched cards, and paper tape, and other peripherals.[9] Real-time service was provided by having each card slot be assigned a fixed interrupt vector that called the appropriate device driver.[5]

As the machine entered the market, it quickly became clear it was selling much more rapidly into the business data processing market than the originally targeted instrumentation market. This led to the introduction of the 2115A in 1967, which removed much of the expansion capabilities to make a lower-cost offering for commercial users. A further simplified version shipped as the 2114A in 1968,[5] which had only eight slots, leaving room for the power supply to be incorporated into the main chassis.[10] The 2115 and 2114 also lacked the extensive DMA control of the 2116, removed some of the mathematical operations, and ran at slightly slower speeds.

These are the original models using core memory and a hardwired CPU:

- 2116A, 10 MHz clock, 1.6-microsecond (μs) cycle time. Normally supplied with 4k words, expandable to 8k internally or 16k with an external memory system. Chassis includes 16 I/O slots, also expandable. Weight 230 pounds (104 kg).[11] Introduced November 1966. It marked HP's first use of integrated circuits.[7]

- 2116B, supported a new 32k memory expansion option. Weight as above.[12] Introduced September 1968.

- 2116C, used smaller core so a full 32k could fit in the main chassis. Introduced October 1970.

- 2115A, short-lived, cost-reduced version that removed the DMA and some math functions, had only 8 I/O slots, and ran at 8 MHz clock and a 2.0 μs cycle time. Weighed 65 pounds (29 kg), required a bulky external power supply – total weight: 160 pounds (72.6 kg).[12] Introduced November 1967.

- 2114A, further simplified 2115 with a new front panel and internal power supply. Non-mechanical touch switches on front panel. Weight 95 pounds (43 kg).[12] Introduced October 1968.

- 2114B, 2114A with a single DMA channel and a new front panel with illuminated push-buttons. Introduced November 1969.

- 2114C, as 2114B with a maximum 16k memory. Introduced October 1970.

HP 2000

[edit]In November 1968[13] the company released the 2000A Timeshare System,[13] later known as HP 2000/Access. This was based on the 2116B (a 2116A with an expanded 8k core memory) running HP Time-Shared BASIC and used a separate 2114 as a terminal server. T-S BASIC allowed multiple user accounts to be created[14] with up to 16 users logged in at once.

Later models of the 2000, B through F, used newer versions of the underlying CPU as they were introduced. Some models used low-end versions of the same CPU as the terminal server; the 2000F, for instance, used a 2100S as the main CPU and primary storage controller, while a 2100A acted as the terminal server.[15] The B, C and F models were dual-processor. In the last version, the 2000F, a 2100S and 2100A CPU were used, with the 2100A connected to up to 32 serial terminals via serial multiplexer interfaces.[15]

In spite of its relatively high costs—the 2000F cost $105,000 in 1974,[15] or about $649,000 in 2023—it was the first minicomputer to offer time-shared BASIC,[16] which made it very popular in the early-to-mid-1970s.

2100

[edit]

Through the 1970s, the lineup was constantly improved with new models that remained compatible in software and expansion with the original 2116.

In early 1970, Fred Allard, formerly of Ampex's Memory Core Division, was asked to design a new magnetic-core memory system for the systems rather than continue purchasing them from Ampex. Using newer 18 mil cores, down from 22 mil, and using a single sense/inhibit line, they fit an 8 kW memory onto a single expansion card. This was used starting in the 2116C models.[18]

In 1971, the updated 2100A replaced the entire existing 211x lineup. The overall system was similar to the earlier models and continued to be based on core memory. Physically, it most resembled the 2114, as the power supply was built-in and it had limited internal expansion. However, the CPU was rebuilt with microcode that could be user-programmed, added hardware multiply and divide, and it added a simple memory protection system, which caused a high-priority interrupt when triggered. A two-channel DMA controller provided higher throughput. An optional floating-point unit was also available. Front panel buttons were illuminated by small incandescent lamps that burned out with use. The use of a switched-mode power supply[a] allowed the chassis to be significantly smaller than the earlier models.

By 1972, HP had shipped 4,500 minis, making it one of the largest companies in the market. That year, they merged the Mountain View Division, which made magnetic tape drives, with the Cupertino Division to create the Data Systems Division (DSD). By this time, the HP 3000 project was in serious trouble, and in February 1973, Packard sent Paul Ely to take over the division. Sales of the 2100 series remained strong; the 6000th shipped in August 1973, the 8000th in February 1974, and its 10,000th in February 1975.[20] They were declared obsolete in 1978.[1]

- 2100A, normally with 4 kW but expandable to 32 kW, 14 I/O slots expandable to 45. Introduced in 1971.

- 2100S, a 2100A bundled with the floating-point option, a time base generator for interfacing with time-dependent hardware, and a teleprinter interface card. Introduced in 1973.

21MX

[edit]In 1972, the division decided to move to 4kbit SRAM memory chips in place of core. These were about twice as fast as contemporary low-cost core, and much smaller, allowing 32kword machines to be built in a 2114-like form factor. At the time they made this decision, 4kbit SRAMs were not actually available, so experimental machines using the core from a 2100 series were used initially, replaced by 1kbit SRAM. At first it appeared 4k parts would not be available by the time the rest of the machine had been upgraded, so the company canvassed various manufacturers and found that a few were aggressively developing 4k parts. In particular, Intel, Mostek, Motorola, and Texas Instruments were all suggesting such parts would be available in quantity by late 1974.[21]

Using such memories in an expansion chassis like the earlier systems meant there was room for much more memory, into the megaword range. However, the CPU's use of 15-bit addresses limited the size to 32kwords.[22] To address the desire for larger systems, HP developed the "Dynamic Mapping System", or DMS. DMS expanded the address format from 15 to 20 bits, allowing a maximum of 1,048,576 words, a dramatic expansion of the original system.[23]

These changes led to the 1974 introduction of the first of the 21MX series machines. This stood for the "21-M" processor and the "21-X" memory, as the memory control systems were separated from the CPU in order to provide flexibility in case the chosen 4k parts were changed during production. This proved useful in practice as the machines were shipped with memories using either Motorola or Texas Instruments parts, and they could be mixed in a single machine, while the higher density system based on 16-pin Mostek parts could be supported by replacing the normal 21-X/2 controller with the 21-X/1.[21]

The entire 2100 series was replaced in 1974 with the first of these 21MX series machines. Using the highest-density parts, the new machines could support up to 1.2 MB in the largest models. When the CPU was further upgraded in 1976, the new models became the "21MX E-Series" and the original models retroactively became the "21MX M-Series". The main difference between the M and E was that the E used clever timing to improve the speed to about twice that of the M.[24] A wider variety of machine styles were released as part of the 21MX series, including smaller systems with four slots and larger ones with 9 or 14 slots.[25]

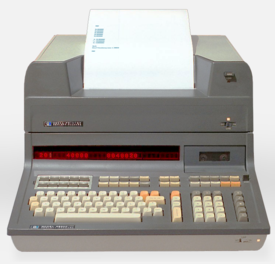

The 21MX series featured a memory management unit and semiconductor memory expandable to 1,048,576 words (one megaword). The bit displays on the front panel buttons used small red light-emitting diodes (LEDs), instead of the burnout-prone incandescent bulbs used in earlier versions.

- M-series – 2105A, 2108A, 2112A (blue line on front panel)

- E-series – 2109A, 2113A (yellow line on front panel; E for extended)

- F-series – 2111F, 2117F (red line on front panel; F for floating-point processor in a separate 2U chassis)

The 21MX ran the HP RTE (real time) operating system (OS). They started out as refrigerator-sized 19-inch rackmount systems with lights and switches on the front panels. The last models would use a 1-chip processor and fit under a desk using a console terminal rather than a front panel.

The new L and A series models had HP-IB interface ability, but as with all HP systems at that time, the blinking LED lights were removed from the front panel. Despite customer demands for a real-time ability and HP R&D's efforts using an installable real-time card, the RTE-A OS was not as good at real-time operations as RTE on a 21MX. This was an important reason this computer was hard to kill. Many companies use real-time operations to take a measurements and control processes—turn on or off a pump, heater, a valve, speed up or slow down a motor, etc.

1000 series

[edit]

At the end of 1977, the entire line was renamed as the "HP 1000", becoming the "HP 1000 M-Series" and "HP 1000 E-Series". The next year the "HP 1000 F-Series" was introduced, which was an E-Series with an added floating point unit.[26] By 1978, the success of the line had propelled HP to become the fourth-largest manufacturer in the minicomputer space, trailing only DEC, IBM, and Data General.[5]

In 1980, the "HP 1000 L-Series" was introduced. This used a new processor based on HP's large-scale integration silicon on sapphire process. Additionally, the expansion cards were also equipped with their own processors that allowed them to access main memory and conduct input/output without bothering the CPU. Although this made the expansion cards incompatible with the earlier models for the first time, it also greatly improved overall performance. These models lacked the memory management unit.[27]

- HP1000L silicon on sapphire (SOS) CPU and I/O processors

The L-Series was, in turn, replaced in 1982 with the "HP 1000 A-Series", which included a new "Lightning" CPU design that reached 1 MIPS, and the even faster "Magic" CPU at 3 MIPS. A wide variety of different models was produced, including desk-side towers, and a variety of different size rack-mount systems.[27] A low-end A400 model was introduced in 1986,[28] and the final high-end A990 released in 1990.[29] Each addressable up to 32 MB of RAM.

- 1981:

- 1982??:

- A700 – based on AMD AM2903 bit-slice processor, optional hardware floating point processor, 1MIPS, 204kFLOPS, microprogramming, optional ECC memory. Codename: PHOENIX

- 1984:

- A900 – Provides pipelined data path, 3MIPS, 500kFLOPS, ECC memory. Codename MAGIC

- 1986:

- A400 – first single-board CPU including 4 serial lines; CPU fabricated by VLSI Technology with their CMOS-40 process, 512 KB RAM on board. Codename Yellowstone

- 1992:

- A990 – CPU implemented with two 208-pin CMOS application-specific integrated circuits (ASICs), 298 instructions, supports up to 512 MB of memory.

| Year | Machine | Microword size |

Microcode size |

Microword types |

ALU |

Carry generator |

Micro sequencer | |

|---|---|---|---|---|---|---|---|---|

| 1973 | 2100S | 24 | 1K | 3 | 4×74181 | 74182 | Discrete | |

| 1974 | 1000 M-Series | 24 | 4K | 4 | 4×74181 | 74182 | Discrete | |

| 1976 | 1000 E-Series | 24 | 16K | 4 | 4×74S181 | 74S182 | Discrete | |

| 1978 | 1000 F-Series | 24 | 16K | 4 | 4×74S181 | 74S182 | Discrete | |

| 19?? | F-Series FPP | ? | ? | ? | 4×74S181 | 74S182 | Discrete | |

| 1980 | 1000 L-Series | ? | ? | ? | Custom CMOS/SOS | |||

| 1981 | 1000 A600 | 56 | 4K | 5 | 4×2901B | 74S182 | 2910+2904 | |

| 1982 | 1000 A700 | 32 | 16K | 11 | 4×2903 | 74S182 | 2911 | |

| 1984 | 1000 A900 | 48 | 32K | 4 | 4×74S381 | 74S182 | Discrete | |

| 1986 | 1000 A400 | 32 | 16K | 11 | Custom CMOS/SOS | |||

| 1975 | 13037 Controller[31] | 24 | 4K | 7 | 4×74S181 | 74S182 | Discrete | |

| 1980 | 13365 Controller | 24 | 3K | ? | 2×2901 | ? | ||

| 1977 | 3000 Series I | 32 | 4K | 5 | 4×74181 | 74182 | Discrete | |

| 1978 | 3000 Series III | 32 | 64K | 5 | 4×74S181 | 74S182 | Discrete | |

| 1978 | 3000 Series 33 | 32 | 6K | ? | Custom CMOS/SOS | |||

| 198? | 3000 Series 48 | 48 | 12K | 2 | 4×74S181 | 74S182 | Discrete | |

| 1982 | 3000 Series 64 | 64 | 8K | ? | 4× 100181 | 100179 | Discrete | |

| 1985 | 3000 Series 37 | 64 | 10K | ? | Custom CMOS gate array | |||

Legacy

[edit]The HP 2000 series was introduced in 1969, sold until June 1978, and was supported until 1985.[32]

Versions of many seminal BASIC games were written on, or ported to, the platform. Notable among these was Mike Mayfield's Star Trek of 1971.[33][34][b] Its popularity made its dialect of BASIC a lingua franca and many BASIC listings were normally provided in that format; the People's Computer Company published their programs in HP 2000 format.[35][36] HP systems were also used for teaching statistics, regression analysis,[37] and economics.[c]

21st century

[edit]The 2000 and 2100 designations have been reused:

Architecture

[edit]Memory organization

[edit]The HP 2100 was designed in an era when RAM in the form of magnetic core memory was falling from dollars to pennies per bit,[40] while implementing processor registers using transistors or small-scale integration remained very expensive. This favored designs with few registers and most storage in RAM, which in turn influenced the instruction set architecture (ISA) to use a memory-memory or memory-accumulator design. This basic concept was first widely introduced in the seminal 12-bit PDP-8, which spawned many similar designs like the 2100.

In the 2100, addresses are 15-bits long, allowing a total of 32k 16-bit words of memory (64 KB in modern terms).[41] The smallest addressable unit of memory is a 16-bit word; it has no instructions that fetch a single 8-bit byte. The address is broken into two parts, the 5 most significant bits refer to one of 32 "pages", while the 10 least significant bits are the "displacement" pointing to a single word within the 1,024-word page. With the DMS system in the 21MX series, the upper 5 bits are instead used to select one of 32 registers, each of which holds 12 bits. The least significant 10 bits of the register are then placed in front of the original 10-bit displacement to produce a 20-bit address.[23] The two most significant bits are used to implement memory protection.[23]

Most processing is handled in the two A and B registers, each 16 bits wide. The registers are also accessible at memory locations 0 and 1, respectively. This means that one can load a value into an accumulator using the normal register-save operation, for instance, LDA 1 will LoaD the value of the A register into memory location 1, thereby copying the value of A into B.[42]

In addition to the A and B registers, the CPU also includes the M register which holds the current memory address, and the T register which holds the value at that address.[43] The P register is used as the program counter and automatically incremented with every instruction, but it is also used as the base address for some memory accesses (see below) that are calculated and placed in M. There are also two one-bit registers, Overflow and Extend,[41] in modern terms, these bits would be considered the status register. Additionally, there is the 16-bit S/D (Switch/Display) register, which is used for input and output from the front panel.[44][45]

Certain areas of memory are reserved for special purposes, like locations 0 and 1 used by the accumulators. Additional words in the lowest 64 locations in memory are used for direct memory access (DMA), and vectored interrupts (see below). In later models, the highest 64 words of available memory are reserved for the boot loader.[46]

Instructions

[edit]| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (bit position) |

| Accumulators | ||||||||||||||||

| A | ||||||||||||||||

| B | ||||||||||||||||

| Program Counter | ||||||||||||||||

| P (page) | P (address) | |||||||||||||||

| Flags | ||||||||||||||||

| O | X | |||||||||||||||

The original instruction set contained 68[5] or 70 instructions.[48]

- Arithmetic – Add, Increment, And, Or, Exclusive or

- Program Control – Skip, Jump, Jump to Subroutine

- Shift and Rotate – Arithmetic and Logical Shifts, 16- and 17-bit Rotates

- Optional – Multiply, Divide, 32-bit Load and Store, 32-bit Shifts

All 68 instructions in the standard instruction set are 16 bits long. Most execute in one memory cycle, or 16 clock cycles,[49] although indirect addressing and the ISZ can use up to 36 cycles.[44] Conditional branching is done with a conditional skip-over-one instruction, that one instruction normally being a jump instruction. There is no stack for subroutines; instead, the first memory location of the routine is reserved, and the return address written to that location by the JSB instruction.[50] This means there is no internal support for re-entrant code; support for this has to be added via a user-implemented stack.

There are three basic styles of instructions in the ISA; memory references, register references, and input/output. Certain models extended the ISA with add-on hardware, adding, for instance, floating point instructions or additional integer math and memory instructions, but these would fall into the same three basic categories.[42]

Memory instructions use four bits for the instruction, and two more for special flags, for a total of six bits of the 16-bit word. This leaves room for a 10-bit address in the instruction, stored in the least significant bits (LSBs), 0 to 9. If bit 15 is set, this indicates "indirect" addressing instead of "direct". In Direct mode, the address in the instruction is the address of the operand, while in Indirect mode, the address was a pointer to another memory location that contained the address of the operand. One could set bit 15 on that location as well, allowing the indirection to be of any required depth, ending when one of the locations has a 0 in bit 15.[41][51]

In addition to the Direct/Indirect mode, bit 10 of the instruction controls the Z/C flag. When set to 0, this means the address's upper five bits were zero while the lower 10 were the value in the instruction. This allows fast access to the Z(ero) page, the first 1,024 words of memory. When set to 1, the address is constructed by combining the 10 bits in the instruction to the top 5 bits of the P register, the C(urrent) page of memory, allowing memory to be accessed as 32 pages of 1024 words.[52] Thus 2,048 words can be addressed at any given time; 1,024 of them within page zero and another 1,024 within the same page as the instruction performing the reference.[51]

Register instructions do not require an address, and thus have more free bits to work with. This is used to pack up four or eight instructions into a single memory word,[53] which, used properly, can significantly speed operations. A total of 39 register operations are included, which are broken down into shift-and-rotate instructions, and the alter-and-skip instructions, indicated by bit 10,[54] while bit 11 indicates whether this is being applied to register A or B.[55]

There are two general classes of register instructions, the shift-and-rotate group and the alter-and-skip. The first is used for basic bitwise manipulation of the values in a register and can have up to four instructions per word, although the two instructions in the middle are always a CLE,SLA/B (clear E, skip if A/B is zero). The second group has eight instructions that perform increments on the registers and then a conditional branch. These are normally used to implement loops.[54]

I/O and interrupts

[edit]Input/Output instructions normally communicate through the accumulators. The instruction format starts with the bits "1000" in the most significant bits, followed by a single bit indicating which register to use (A=0, B=1), followed by a "1", the H/C flag bit, and then three bits for the instruction and the remaining six bits for the I/O device ID,[56] or channel, allowing up to 64 devices. Some device numbers are used by the system itself.[57]

I/O is initiated by clearing the Flag bit with STF and then setting the C bit using STC. The hardware notices this pattern and begins its operation. When the operation is complete, the device sets the Flag bit and then the program loads the resulting data from the card using the LI* instruction, or sends it to the card with OT*.[56]

The actual data transfer is normally accomplished using the interrupt system. Memory locations 4 through 63 (decimal) hold the addresses of routines to jump to when an interrupt is fired, providing 60 interrupt levels.[58] Location 4 through 7 are hard-wired to power failures, parity check errors, and in later models memory protection errors. Locations 8 and up are user-accessible interrupt vectors, mapped to an I/O channel and arranged in priority order.[59] So if I/O device 13 produced an interrupt, the CPU jumps to the location in memory location 13, but only if it is not masked out by a higher-priority interrupt, 1 to 12.[58]

Another key feature of the 2100 series is a separate direct memory access controller that uses cycle stealing to access memory when the CPU is not using it, during the times when it is performing internal calculations for instance. Using this feature, lengthy I/O processes can be completed while the CPU works on other problems. The system is set up by sending an instruction to the DMA controller using the I/O commands; the DMA controller is channel 6, and is initially sent an instruction containing the number of the I/O device that wants to use DMA, whether it is an input (write to memory from device) or output (read from memory to device), the starting location in memory for the data, and the number of words. This setup code is often installed into one of the interrupt vectors, automating the process.[57] The DMS has separate tables for the CPU and DMA system, so DMA can load data into separate parts of extended memory.[23]

Programming

[edit]HP supplied a three-pass assembler for the machine,[60] using a column-delimited format. The first area, on the left of the line of code, is the label, which has to start in column 1 if present. Next comes the instruction mnemonic, then the parameters. The rest of the line can be used for a comment. The assembler allows basic mathematical expressions to be written directly, instead of using mnemonics, and also includes a number of pseudo-instructions like ORG to set the base address of the program.[56]

In addition to the assembler and associated linker, the machines initially shipped with a FORTRAN 66 compiler, the operating system, and I/O drivers. Over time, additional languages were added including BASIC, ALGOL, FORTRAN IV[61] and FORTRAN 77.[62]

HP ported implementations of AGL to the platform, which added commands to their BASIC to produce graphics on their graphics terminals and plotters. A similar expansion in their FORTRAN was called GRAPHICS/1000.

Operating systems

[edit]The 2100s were normally used with the "Real Time Executive" operating system, or RTE for short.[63] Several versions of RTE were released for the different versions of the machine; RTE-II for the 2114-2116, RTE-III for the 2100s, RTE-IV for the 21MX series, and RTE-A for the "A" series.

The operating system shell, even in the late 1970s, was very primitive, with a single-level file system, File Manager, or FMGR. For example, the command to run a FORTRAN compiler would be as follows:[62]

ru, f77, &test,'test,%test

meaning run the f77 program, using special characters to distinguish between source file, object, and executable files.

The HP 1000 also was one of the few minicomputers that restricted file names to only five characters, rather than the six common at the time, which made porting and even writing programs a challenge. The later RTE-A for HP 1000 provided conventional directory structure with 16.4 file names, and made the ru command optional.

TODS (Test Oriented Disk System) was developed by a technician at the HP board repair center to improve turn-around time in the center. It was used to load diagnostics from a central repository as opposed to loading individual paper tapes. TODS was also used on HP 2116 thru 21MX-F series for test systems for missiles such as Phoenix (9206B), Harpoon (9500D-354), Tomahawk, and many others. Early test sets were the 9500A, evolving to the 9500D, followed by the ATS (Automated Test System); specific HP test systems, such as the 9500D-A46 Minuteman launch component test set and ATS-E35 Peacekeeper/Minuteman launch component test set; the HP 8580/8542 Microwave ANA/ASA (Automatic Network Analyzer / Automated Spectrum Analyzer) ran on TODS; and the TDRSS microwave transponder test set used TODS and was a very large system.

There was also MTOS (Magnetic Tape Operating System) similar to TODS.

Descendants and variants

[edit]This section's factual accuracy is disputed. (December 2013) |

The HP 9810, 9820, and 9830 desktop computers use a slow, serialized TTL version of the 2116 CPU, although they did not ultimately use any of the operating system or application software, instead relying on user-friendly ROM-based interpreters, such as BASIC, which work when powered up, and integrated keyboards and displays rather than disks or standard terminals. In 1975, HP introduced the BPC (Binary Processing Chip), one of the world's first 16-bit microprocessors, using HP's NMOS-II process.[64][65] The BPC was usually packaged in a ceramic hybrid module with the EMC and IOC chips, which added extended math and I/O instructions. The hybrid was developed as the heart of the new 9825 desktop computer.[66] The later 9845 workstation added an MMU chip. These were the forerunners of personal computers and technical workstations.

The major differences between the original 2116 architecture and the BPC microprocessor are a completely redesigned I/O structure, the removal of multiple levels of indirect addressing, and the provision of a stack register for subroutine call and return. The elimination of multiple indirection made an additional bit available in a memory word containing an indirect address, allowing the maximum memory capacity to be increased from 32K 16-bit words to 64K. The BPC also added an input allowing the "current page" to be relative to the location of the current instruction, rather than a power-of-two aligned page.

The BPC was used in a wide range of HP computers, peripherals, and test equipment, until it was discontinued in the late 1980s.

Poland manufactured an HP 2114B clone since 1973. The Polish clones were called MKJ-28 (prototype, 1973), SMC-3 (pilot production, 17 machines, 1975-1977), and PRS-4 (production in series over 150 machines, 1978-1987).

Czechoslovakia produced its own HP 1000 compatible clones, designated ADT4000 (4300, 4500, 4700, 4900). The vendors Aritma Prague (development), ZPA Čakovice, and ZPA Trutnov delivered more than 1,000 units between 1973 and 1990. Those computers served in power plants, including nuclear ones, other industry, military, at universities, etc., for their high reliability and real-time features. Operating systems were DOS/ADT (several versions) and Unix. The oldest hybrid ADT7000 (1974) was composed of digital ADT4000 and analog ADT3000 parts, but only the digital part was interesting for customers. ADT4316 (1976) had 16K words of ferrite core memory, the ADT4500 (1978) up to 4M words of semiconductor RAM. The ADT 4900 was designed as a single-board computer, but its mass production did not start. Czechoslovak People's Army used ADT-based MOMI 1 and MOMI 2 mobile minicomputers, built into a container carried by the Tatra 148 truck.

Notes

[edit]- ^ Claimed to be the first example of such in a computer.[19]

- ^ The original version of Star Trek was written the same year for the SDS Sigma 7 mainframe, but the source code was lost when he lost access to that machine. It was re-written from scratch on the HP 2000, which remains the earliest publicly available version.

- ^ GMCRO1: Macroeconomics; BitSavers

References

[edit]Citations

[edit]- ^ a b "2100A".

- ^ "21-MX".

- ^ "1000, L/A Series".

- ^ "1000 A990".

- ^ a b c d e f g h i Leibson 2017.

- ^ "Dymec".

- ^ a b "History of the 2116A digital computer". HP.

- ^ "50th Anniversary of HP's First Computer".

- ^ HP 1967, p. 2-16.

- ^ "2114".

- ^ HP 1967, p. 2-2 (9).

- ^ a b c "Hewlett-Packard First Generation Computer Census - The Vintage Technology Association". decadecounter.com. HP computers brochures, HP 2116/15/14 Differential Specifications. Archived from the original on December 29, 2009. Retrieved 2019-02-06.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b "Hewlett/Packard Computers".

The 2000A was the first HP 2000 time share system on the market ca. 1969

- ^ User IDs were a letter followed by 3 digits, allowing up to 26,000 user accounts.

- ^ a b c "2000 Timeshare System".

- ^ "Passing the 10-year mark". MEASURE Magazine. Hewlett Packard. October 1976.

- ^ "Computing at ESO Through the Ages - The amazing advance of technology". ESO Picture of the Week. Retrieved 4 June 2012.

- ^ "2116".

- ^ Poynor, Todd (August 1991). "25 Years of Real-Time Computing" (PDF). REAL-TIME Interface. HP-Interex.

- ^ "Mountain View".

- ^ a b Frankenberg 1974, p. 16.

- ^ HAYES, JOHN P. (1978). Computer Architecture and Organization. p. 303. ISBN 0-07-027363-4.

- ^ a b c d Frankenberg 1974, p. 19.

- ^ "21MX E-Series".

- ^ "21MX M-Series".

- ^ "21MX F-Series".

- ^ a b "1000, L/A Series".

- ^ "1000 A400".

- ^ "1000 A990".

- ^ Bryan, J. David. "HP Features" (Document). HP.

- ^ "13037-60023 Disc Controller Interface". 1000 — 21MX. HP Computer Museum.

- ^ "2000 Timeshare System".

- ^ The Best of Creative Computing, Volume 1. Creative Computing. 1976. p. 275.

- ^ "STTR1: STAR TREK, HP BASIC PROGRAM LIBRARY". Archived from the original on 2015-02-15.

- ^ What to do after hitting Return. People's Computer Company. 1975. p. vii.

- ^ Albrecht, Bob (1972). My Computer Likes Me When I Speak in BASIC. Dymax.

- ^ Robert F. Ling; Harry V. Roberts (Jul 1975). "IDA: An Approach to Interactive Data Analysis in Teaching". The Journal of Business. 48 (3): 411–451. doi:10.1086/295765. JSTOR 2352233.

- ^ John R. Delaney. "HP 2000-2b19wm Review & Rating". PC Magazine. Archived from the original on 2019-01-26. Retrieved 2018-11-09.

The HP 2000-2b19wm .. a 15-inch laptop for under $300

- ^ "HP LaserJet 2100 Printer series Software and Driver Downloads". HP Support. Retrieved 8 March 2024.

- ^ "Memory Prices (1957-2017)". John C. McCallum.

- ^ a b c Peterson 2014, p. 371.

- ^ a b Peterson 2014, p. 370.

- ^ HP 1967, p. 2-4.

- ^ a b HP 1967, p. 2-5.

- ^ 2100 1972, pp. 2–7, 2–8.

- ^ 2100 1972, p. 2-6.

- ^ 2116C Computer, Volume 1 (PDF). Hewlett-Packard. July 1971. p. 2-4. Retrieved 16 January 2024.

- ^ "HP 2114/15/16 brochure cover". Computer History Museum.

- ^ HP 1967, p. 2-2.

- ^ Peterson 2014, p. 372.

- ^ a b HP 1967, pp. 2–3.

- ^ Peterson 2014, pp. 371–372.

- ^ HP 1967, p. 2-9.

- ^ a b HP 1967, p. 2-11.

- ^ HP 1967, pp. 2–10, 2–11.

- ^ a b c Peterson 2014, p. 375.

- ^ a b Peterson 2014, p. 377.

- ^ a b HP 1967, p. 2-12.

- ^ HP 1967, p. 2-6.

- ^ Peterson 2014, p. 374.

- ^ HP 1967, p. 1-7.

- ^ a b Fortran 77 manual

- ^ Weisenberg, Michael (28 June 1982). "Systems with mainframe power come in micro sizes". InfoWorld. p. 25.

- ^ Eads, William D.; Maitland, David S. (June 1976). "High-Performance NMOS LSI Processor" (PDF). HP Journal. 27 (10): 15–18.

- ^ Leibson, Steve. "Hybrid Microprocessor". HP9825.COM. Retrieved 2008-06-15.

- ^ US 4075679, "Programmable calculator", published 1978-02-21, assigned to Hewlett-Packard Company

Bibliography

[edit]- Leibson, Steve (2017). "HP: The Accidentally, On-Purpose Computer Company". HP9825.COM.

- The Hewlett Packard Company. HP1000/RTE Home page.

- Hewlett-Packard (March 1967). "Section 2-26, Direct/Indirect". HP 2116A Computer Specifications and Basic Operation, Volume 1 (PDF). pp. 2–3.

- Peterson, James (2014). "Section 2-26, Direct/Indirect". Computer Organization and Assembly Language Programming. Academic Press. pp. 369–378. ISBN 978-1-4832-6859-0.

- Guide to the 2100 Computer. Hewlett-Packard. September 1972.

- Frankenberg, Robert (October 1974). "All Semiconductor Memory Selected for New Minicomputer Series" (PDF). Hewlett-Packard Journal. 26 (2): 15–20.

External links

[edit]- Jeff Moffat's HP2100 Archive: software and manuals

- Simulator, with executable binaries and source in C

- 1972 HP 2100 Brochure

- Rack-mounted HP2100 system Guilherme Bittencourt's site image showing from top to bottom, left: a 21MX E-series computer, 2100A computer, 2100 power supply (PS), 7905 disc drive, 13037 drive controller; right: paper tape reader, paper tape punch, 7900 disk drive, 7900 PS.

- HP Computer Museum: 1000-L & A Series

- Computer History Museum: The HP Way, HP 2116, Year 1966.