Arithmetic logic unit

| Part of a series on | |||||||

| Arithmetic logic circuits | |||||||

|---|---|---|---|---|---|---|---|

| Quick navigation | |||||||

|

Components

|

|||||||

|

See also |

|||||||

In computing, an arithmetic logic unit (ALU) is a combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers.[1][2] This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs).[3]

The inputs to an ALU are the data to be operated on, called operands, and a code indicating the operation to be performed; the ALU's output is the result of the performed operation. In many designs, the ALU also has status inputs or outputs, or both, which convey information about a previous operation or the current operation, respectively, between the ALU and external status registers.

Signals

[edit]An ALU has a variety of input and output nets, which are the electrical conductors used to convey digital signals between the ALU and external circuitry. When an ALU is operating, external circuits apply signals to the ALU inputs and, in response, the ALU produces and conveys signals to external circuitry via its outputs.

Data

[edit]A basic ALU has three parallel data buses consisting of two input operands (A and B) and a result output (Y). Each data bus is a group of signals that conveys one binary integer number. Typically, the A, B and Y bus widths (the number of signals comprising each bus) are identical and match the native word size of the external circuitry (e.g., the encapsulating CPU or other processor).

Opcode

[edit]The opcode input is a parallel bus that conveys to the ALU an operation selection code, which is an enumerated value that specifies the desired arithmetic or logic operation to be performed by the ALU. The opcode size (its bus width) determines the maximum number of distinct operations the ALU can perform; for example, a four-bit opcode can specify up to sixteen different ALU operations. Generally, an ALU opcode is not the same as a machine language instruction, though in some cases it may be directly encoded as a bit field within such instructions.

Status

[edit]Outputs

[edit]The status outputs are various individual signals that convey supplemental information about the result of the current ALU operation. General-purpose ALUs commonly have status signals such as:

- Carry-out, which conveys the carry resulting from an addition operation, the borrow resulting from a subtraction operation, or the overflow bit resulting from a binary shift operation.

- Zero, which indicates all bits of Y are logic zero.

- Negative, which indicates the result of an arithmetic operation is negative.

- Overflow, which indicates the result of an arithmetic operation has exceeded the numeric range of Y.

- Parity, which indicates whether an even or odd number of bits in Y are logic one.

Inputs

[edit]The status inputs allow additional information to be made available to the ALU when performing an operation. Typically, this is a single "carry-in" bit that is the stored carry-out from a previous ALU operation.

Circuit operation

[edit]

An ALU is a combinational logic circuit, meaning that its outputs will change asynchronously in response to input changes. In normal operation, stable signals are applied to all of the ALU inputs and, when enough time (known as the "propagation delay") has passed for the signals to propagate through the ALU circuitry, the result of the ALU operation appears at the ALU outputs. The external circuitry connected to the ALU is responsible for ensuring the stability of ALU input signals throughout the operation, and for allowing sufficient time for the signals to propagate through the ALU circuitry before sampling the ALU outputs.

In general, external circuitry controls an ALU by applying signals to the ALU inputs. Typically, the external circuitry employs sequential logic to generate the signals that control ALU operation. The external sequential logic is paced by a clock signal of sufficiently low frequency to ensure enough time for the ALU outputs to settle under worst-case conditions (i.e., conditions resulting in the maximum possible propagation delay).

For example, a CPU starts an addition operation by routing the operands from their sources (typically processor registers) to the ALU's operand inputs, while simultaneously applying a value to the ALU's opcode input that configures it to perform an addition operation. At the same time, the CPU enables the destination register to store the ALU output (the resulting sum from the addition operation) upon operation completion. The ALU's input signals, which are held stable until the next clock, are allowed to propagate through the ALU and to the destination register while the CPU waits for the next clock. When the next clock arrives, the destination register stores the ALU result and, since the ALU operation has completed, the ALU inputs may be set up for the next ALU operation.

Functions

[edit]A number of basic arithmetic and bitwise logic functions are commonly supported by ALUs. Basic, general purpose ALUs typically include these operations in their repertoires:[1][2][4]

Arithmetic operations

[edit]- Add: A and B are summed and the sum appears at Y and carry-out.

- Add with carry: A, B and carry-in are summed and the sum appears at Y and carry-out.

- Subtract: B is subtracted from A (or vice versa) and the difference appears at Y and carry-out. For this function, carry-out is effectively a "borrow" indicator. This operation may also be used to compare the magnitudes of A and B; in such cases the Y output may be ignored by the processor, which is only interested in the status bits (particularly zero and negative) that result from the operation.

- Subtract with borrow: B is subtracted from A (or vice versa) with borrow (carry-in) and the difference appears at Y and carry-out (borrow out).

- Two's complement: A (or B) is subtracted from zero and the difference appears at Y.

- Increment: A (or B) is increased by one and the resulting value appears at Y.

- Decrement: A (or B) is decreased by one and the resulting value appears at Y.

Bitwise logical operations

[edit]- AND: the bitwise AND of A and B appears at Y.

- OR: the bitwise OR of A and B appears at Y.

- Exclusive-OR: the bitwise XOR of A and B appears at Y.

- Ones' complement: all bits of A (or B) are inverted and appear at Y.

Bit shift operations

[edit]| Type | Left | Right |

|---|---|---|

| Arithmetic shift |

|

|

| Logical shift |

|

|

| Rotate |

|

|

| Rotate through carry |

|

|

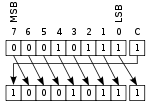

ALU shift operations cause operand A (or B) to shift left or right (depending on the opcode) and the shifted operand appears at Y. Simple ALUs typically can shift the operand by only one bit position, whereas more complex ALUs employ barrel shifters that allow them to shift the operand by an arbitrary number of bits in one operation. In all single-bit shift operations, the bit shifted out of the operand appears on carry-out; the value of the bit shifted into the operand depends on the type of shift.

- Arithmetic shift: the operand is treated as a two's complement integer, meaning that the most significant bit is a "sign" bit and is preserved.

- Logical shift: a logic zero is shifted into the operand. This is used to shift unsigned integers.

- Rotate: the operand is treated as a circular buffer of bits in which its least and most significant bits are effectively adjacent.

- Rotate through carry: the carry bit and operand are collectively treated as a circular buffer of bits.

Other operations

[edit]- Pass through: all bits of A (or B) appear unmodified at Y. This operation is typically used to determine the parity of the operand or whether it is zero or negative, or to copy the operand to a processor register.

Applications

[edit]Status usage

[edit]

Upon completion of each ALU operation, the ALU's status output signals are usually stored in external registers to make them available for future ALU operations (e.g., to implement multiple-precision arithmetic) and for controlling conditional branching. The bit registers that store the status output signals are often collectively treated as a single, multi-bit register, which is referred to as the "status register" or "condition code register".

Depending on the ALU operation being performed, some status register bits may be changed and others may be left unmodified. For example, in bitwise logical operations such as AND and OR, the carry status bit is typically not modified as it is not relevant to such operations.

In CPUs, the stored carry-out signal is usually connected to the ALU's carry-in net. This facilitates efficient propagation of carries (which may represent addition carries, subtraction borrows, or shift overflows) when performing multiple-precision operations, as it eliminates the need for software-management of carry propagation (via conditional branching, based on the carry status bit).

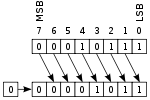

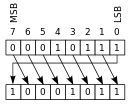

Multiple-precision arithmetic

[edit]In integer arithmetic computations, multiple-precision arithmetic is an algorithm that operates on integers which are larger than the ALU word size. To do this, the algorithm treats each integer as an ordered collection of ALU-size fragments, arranged from most-significant (MS) to least-significant (LS) or vice versa. For example, in the case of an 8-bit ALU, the 24-bit integer 0x123456 would be treated as a collection of three 8-bit fragments: 0x12 (MS), 0x34, and 0x56 (LS). Since the size of a fragment exactly matches the ALU word size, the ALU can directly operate on this "piece" of operand.

The algorithm uses the ALU to directly operate on particular operand fragments and thus generate a corresponding fragment (a "partial") of the multi-precision result. Each partial, when generated, is written to an associated region of storage that has been designated for the multiple-precision result. This process is repeated for all operand fragments so as to generate a complete collection of partials, which is the result of the multiple-precision operation.

In arithmetic operations (e.g., addition, subtraction), the algorithm starts by invoking an ALU operation on the operands' LS fragments, thereby producing both a LS partial and a carry out bit. The algorithm writes the partial to designated storage, whereas the processor's state machine typically stores the carry out bit to an ALU status register. The algorithm then advances to the next fragment of each operand's collection and invokes an ALU operation on these fragments along with the stored carry bit from the previous ALU operation, thus producing another (more significant) partial and a carry out bit. As before, the carry bit is stored to the status register and the partial is written to designated storage. This process repeats until all operand fragments have been processed, resulting in a complete collection of partials in storage, which comprise the multi-precision arithmetic result.

In multiple-precision shift operations, the order of operand fragment processing depends on the shift direction. In left-shift operations, fragments are processed LS first because the LS bit of each partial—which is conveyed via the stored carry bit—must be obtained from the MS bit of the previously left-shifted, less-significant operand. Conversely, operands are processed MS first in right-shift operations because the MS bit of each partial must be obtained from the LS bit of the previously right-shifted, more-significant operand.

In bitwise logical operations (e.g., logical AND, logical OR), the operand fragments may be processed in any arbitrary order because each partial depends only on the corresponding operand fragments (the stored carry bit from the previous ALU operation is ignored).

Complex operations

[edit]Although it is possible to design ALUs that can perform complex functions, this is usually impractical due to the resulting increases in circuit complexity, power consumption, propagation delay, cost and size. Consequently, ALUs are typically limited to simple functions that can be executed at very high speeds (i.e., very short propagation delays), with more complex functions being the responsibility of external circuitry. For example:

- In simple cases in which a CPU contains a single ALU, the CPU typically implements a complex operation by orchestrating a sequence of ALU operations according to a software algorithm.

- More specialized architectures may use multiple ALUs to accelerate complex operations. In such systems, the ALUs are often pipelined, with intermediate results passing through ALUs arranged like a factory production line. Performance is greatly improved over that of a single ALU because all of the ALUs operate concurrently and software overhead is significantly reduced.

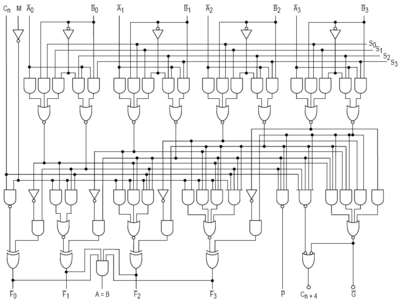

Implementation

[edit]An ALU is usually implemented either as a stand-alone integrated circuit (IC), such as the 74181, or as part of a more complex IC. In the latter case, an ALU is typically instantiated by synthesizing it from a description written in VHDL, Verilog or some other hardware description language. For example, the following VHDL code describes a very simple 8-bit ALU:

entity alu is

port ( -- the alu connections to external circuitry:

A : in signed(7 downto 0); -- operand A

B : in signed(7 downto 0); -- operand B

OP : in unsigned(2 downto 0); -- opcode

Y : out signed(7 downto 0)); -- operation result

end alu;

architecture behavioral of alu is

begin

case OP is -- decode the opcode and perform the operation:

when "000" => Y <= A + B; -- add

when "001" => Y <= A - B; -- subtract

when "010" => Y <= A - 1; -- decrement

when "011" => Y <= A + 1; -- increment

when "100" => Y <= not A; -- 1's complement

when "101" => Y <= A and B; -- bitwise AND

when "110" => Y <= A or B; -- bitwise OR

when "111" => Y <= A xor B; -- bitwise XOR

when others => Y <= (others => 'X');

end case;

end behavioral;

History

[edit]Mathematician John von Neumann proposed the ALU concept in 1945 in a report on the foundations for a new computer called the EDVAC.[5]

The cost, size, and power consumption of electronic circuitry was relatively high throughout the infancy of the Information Age. Consequently, all early computers had a serial ALU that operated on one data bit at a time although they often presented a wider word size to programmers. The first computer to have multiple parallel discrete single-bit ALU circuits was the 1951 Whirlwind I, which employed sixteen such "math units" to enable it to operate on 16-bit words.

In 1967, Fairchild introduced the first ALU-like device implemented as an integrated circuit, the Fairchild 3800, consisting of an eight-bit arithmetic unit with accumulator. It only supported adds and subtracts but no logic functions.[6]

Full integrated-circuit ALUs soon emerged, including four-bit ALUs such as the Am2901 and 74181. These devices were typically "bit slice" capable, meaning they had "carry look ahead" signals that facilitated the use of multiple interconnected ALU chips to create an ALU with a wider word size. These devices quickly became popular and were widely used in bit-slice minicomputers.

Microprocessors began to appear in the early 1970s. Even though transistors had become smaller, there was sometimes insufficient die space for a full-word-width ALU and, as a result, some early microprocessors employed a narrow ALU that required multiple cycles per machine language instruction. Examples of this includes the popular Zilog Z80, which performed eight-bit additions with a four-bit ALU.[7] Over time, transistor geometries shrank further, following Moore's law, and it became feasible to build wider ALUs on microprocessors.

Modern integrated circuit (IC) transistors are orders of magnitude smaller than those of the early microprocessors, making it possible to fit highly complex ALUs on ICs. Today, many modern ALUs have wide word widths, and architectural enhancements such as barrel shifters and binary multipliers that allow them to perform, in a single clock cycle, operations that would have required multiple operations on earlier ALUs.

ALUs can be realized as mechanical, electro-mechanical or electronic circuits[8][failed verification] and, in recent years, research into biological ALUs has been carried out[9][10] (e.g., actin-based).[11]

See also

[edit]- Adder (electronics)

- Address generation unit (AGU)

- Binary multiplier

- Execution unit

- Load–store unit

- Status register

References

[edit]- ^ a b Atul P. Godse; Deepali A. Godse (2009). "3". Digital Logic Design. Technical Publications. pp. 9–3. ISBN 978-81-8431-738-1.[permanent dead link]

- ^ a b Atul P. Godse; Deepali A. Godse (2009). "Appendix". Digital Logic Circuits. Technical Publications. pp. C–1. ISBN 978-81-8431-650-6.[permanent dead link]

- ^ "1. An Introduction to Computer Architecture - Designing Embedded Hardware, 2nd Edition [Book]". www.oreilly.com. Retrieved 2020-09-03.

- ^ Horowitz, Paul; Winfield Hill (1989). "14.1.1". The Art of Electronics (2nd ed.). Cambridge University Press. pp. 990–. ISBN 978-0-521-37095-0.

- ^ Philip Levis (November 8, 2004). "Jonathan von Neumann and EDVAC" (PDF). cs.berkeley.edu. pp. 1, 3. Archived from the original (PDF) on September 23, 2015. Retrieved January 20, 2015.

- ^ Sherriff, Ken. "Inside the 74181 ALU chip: die photos and reverse engineering". Ken Shirriff's blog. Retrieved 7 May 2024.

- ^ Ken Shirriff. "The Z-80 has a 4-bit ALU. Here's how it works." 2013, righto.com

- ^ Reif, John H. (2009), "Mechanical Computing: The Computational Complexity of Physical Devices", in Meyers, Robert A. (ed.), Encyclopedia of Complexity and Systems Science, New York, NY: Springer, pp. 5466–5482, doi:10.1007/978-0-387-30440-3_325, ISBN 978-0-387-30440-3, retrieved 2020-09-03

- ^ Lin, Chun-Liang; Kuo, Ting-Yu; Li, Wei-Xian (2018-08-14). "Synthesis of control unit for future biocomputer". Journal of Biological Engineering. 12 (1): 14. doi:10.1186/s13036-018-0109-4. ISSN 1754-1611. PMC 6092829. PMID 30127848.

- ^ Gerd Hg Moe-Behrens. "The biological microprocessor, or how to build a computer with biological parts".

- ^ Das, Biplab; Paul, Avijit Kumar; De, Debashis (2019-08-16). "An unconventional Arithmetic Logic Unit design and computing in Actin Quantum Cellular Automata". Microsystem Technologies. 28 (3): 809–822. doi:10.1007/s00542-019-04590-1. ISSN 1432-1858. S2CID 202099203.

Further reading

[edit]- Hwang, Enoch (2006). Digital Logic and Microprocessor Design with VHDL. Thomson. ISBN 0-534-46593-5.

- Stallings, William (2006). Computer Organization & Architecture: Designing for Performance (7th ed.). Pearson Prentice Hall. ISBN 0-13-185644-8.